# ELECTRÓNICA DIGITAL Tema 10

Operaciones y circuitos aritméticos

Enrique Mandado Pérez

#### **CONCEPTOS GENERALES**

En la mayoría de los sistemas digitales, desde el circuito de control más sencillo hasta el computador o el sistema de comunicaciones más complejo, se realizan operaciones aritméticas.

En este tema se describen los circuitos aritméticos básicos. El desarrollo de la Microelectrónica ha propiciado el desarrollo de numerosos circuitos aritméticos de mayor complejidad que tardan menos tiempo en ejecutar las diferentes operaciones. Un estudio de los mismos se sale fuera de los límites de este tema y se remite al lector a la bibliografia.

[ERCE 04] M. D. Ercegovac, T. Lang. Digital arithmetic. Morgan Kaufmann. 2004

[FLYN 01] M. Flynn. S. F. Oberman. Advanced computer arithmetic design.

John Wiley & Sons Inc. 2001

[PARH 00] B. Parhami. Computer arithmetic. Algorithms and hardware designs.

Oxford University Press. 2000

### SUMA ARITMÉTICA EN BINARIO NATURAL (BINARY ADDITION)

| Suma | indos | Suma<br>binaria | Acarreo |  |  |

|------|-------|-----------------|---------|--|--|

| 0    | 0     | 0               | 0       |  |  |

| 0    | 1     | 1               | 0       |  |  |

| 1    | 0     | 1               | 0       |  |  |

| 1    | 1     | 0               | 1       |  |  |

Tabla de verdad de la suma aritmética en el sistema de numeración binario

#### OPERACIONES EN EL SISTEMA DE NUMERACIÓN BINARIO SUMA ARITMÉTICA EN BINARIO NATURAL

| $\boldsymbol{b}_0$ | $a_0$ | S | C |

|--------------------|-------|---|---|

| 0                  | 0     | 0 | 0 |

|                    |       |   |   |

| 0                  | 1     | 1 | 0 |

|                    |       |   |   |

| 1                  | 0     | 1 | 0 |

|                    |       |   |   |

| 1                  | 1     | 0 | 1 |

|                    |       |   |   |

$$S_{i} = a_{i} \, \overline{b}_{i} + \overline{a}_{i} \, b_{i} = \overline{a_{i} \, b_{i} + \overline{a}_{i} \, \overline{b}_{i}} = a_{i} \oplus b_{i}$$

$$C_{i+1} = a_{i} \, b_{i} = \overline{\overline{a_{i} \, b_{i}}} = \overline{\overline{a_{i} \, b_{i}}} = \overline{\overline{a_{i} + \overline{b_{i}}}}$$

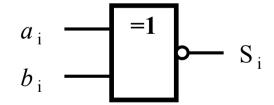

### Circuito semisumador (Half adder)

$$\begin{bmatrix} \overline{a}_i \\ \overline{b}_i \end{bmatrix} \ge 1$$

$C_{i+1}$

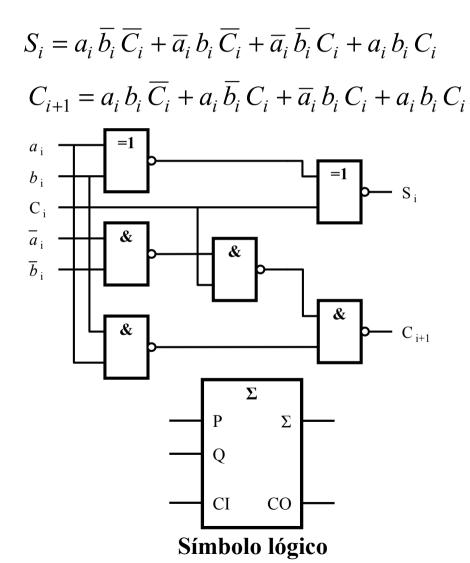

### SUMADOR TOTAL (FULL ADDER)

| $C_{\rm i}$ | $b_{\rm i}$ | $a_{\rm i}$ | S | $C_{i+1}$ |

|-------------|-------------|-------------|---|-----------|

|             |             |             |   |           |

| 0           | 0           | 0           | 0 | X         |

| 0           | 0           | 1           | 1 | X         |

| 0           | 1           | 0           | 1 | 0         |

| 0           | 1           | 1           | 0 | 1         |

| 1           | 0           | 0           | 1 | 0         |

| 1           | 0           | 1           | 0 | 1         |

| 1           | 1           | 0           | 0 | 1         |

| 1           | 1           | 1           | 1 | 1         |

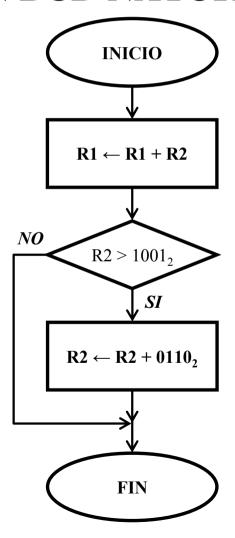

#### SUMA DE NÚMEROS DE VARIOS BITS

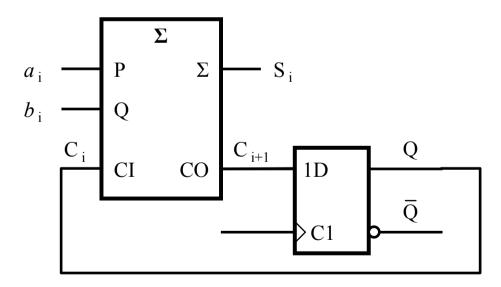

- En serie (Serial binary adder), utilizando un único sumador total.

- En paralelo (Paralell binary adder), utilizando tantos sumadores totales como bits se tienen que sumar.

#### SUMADOR EN SERIE DE VARIOS BITS

El avance de la Microelectrónica ha hecho que ya no se utilice

#### SUMADOR EN PARALELO DE VARIOS BITS

- Sumador con generación del acarreo en serie (Ripple adder)

- Sumador con generación del acarreo en paralelo (Carry lookahead adder)

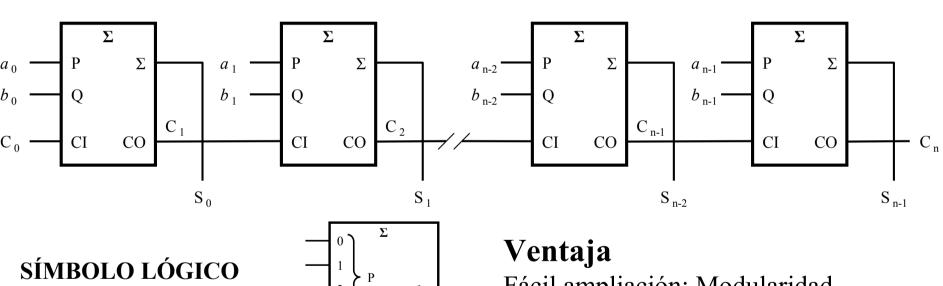

#### OPERACIONES EN EL SISTEMA DE NUMERACIÓN BINARIO SUMADOR EN PARALELO DE VARIOS BITS

Sumador con generación del acarreo en serie

**NORMALIZADO**

Fácil ampliación: Modularidad

#### Desventaja

Lentitud: El tiempo que tarda en sumar depende del número de bits

#### SUMADOR EN PARALELO DE VARIOS BITS

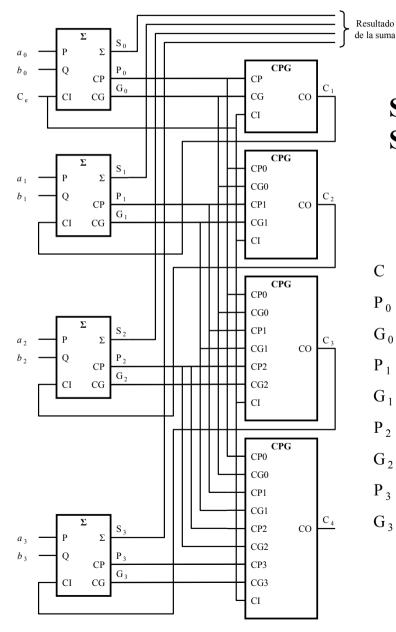

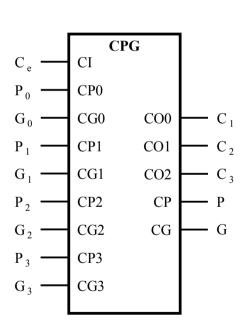

Sumador con generación del acarreo en paralelo

(Carry lookahead adder)

$$C_{i+1} = a_i b_i + (a_i + b_i) C_i$$

$$C_{i+1} = G_i + P_i C_i$$

G: Carry generator (CG)

P: Carry propagator (CP)

Ecuación del acarreo en paralelo de las n etapas de un sumador de n bits. Si se denomina  $C_e$  al acarreo que se aplica a la primera etapa, resulta:

$$C_1 = G_0 + P_0 C_e$$

En la segunda etapa:

$$C_2 = G_1 + P_1 C_1 = G_1 + P_1 G_0 + P_1 P_0 C_e$$

$$C_{\rm n} = G_{\rm n-1} + P_{\rm n-1}G_{\rm n-2} + P_{\rm n-1}P_{\rm n-2}G_{\rm n-3} + \dots + P_{\rm n-1}P_{\rm n-2}\dots P_{\rm 1}G0 + P_{\rm n-1}P_{\rm n-2}\dots P_{\rm 1}P_{\rm 0}C_{\rm e}$$

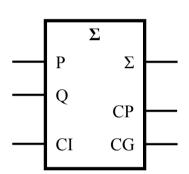

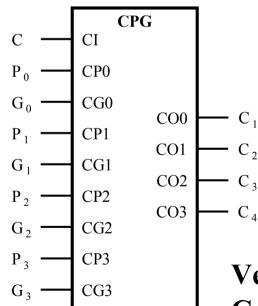

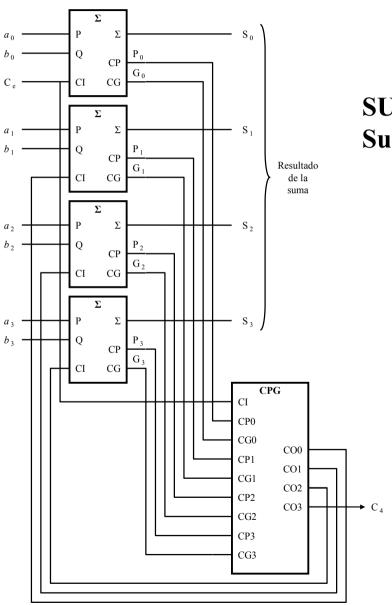

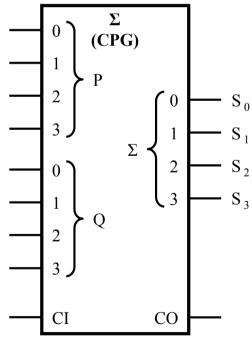

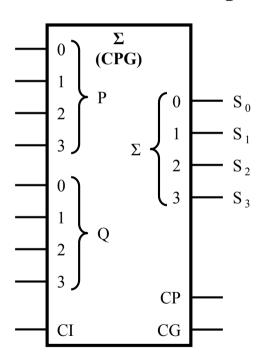

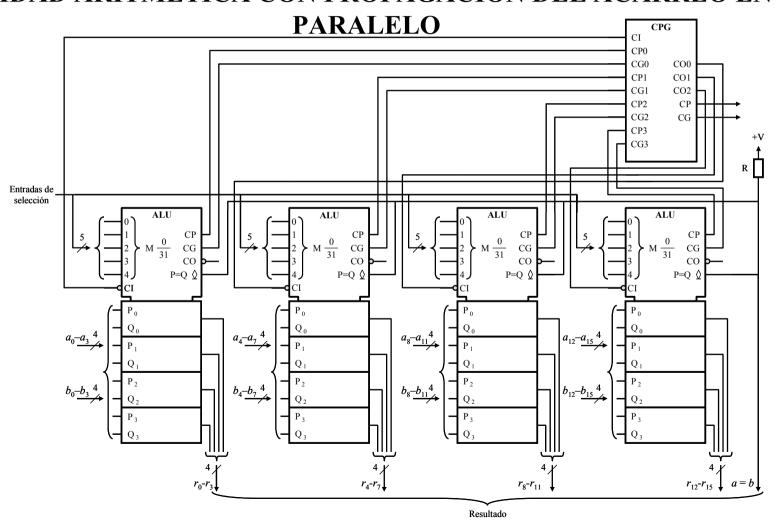

**SUMADOR EN PARALELO DE VARIOS BITS Sumador con generación del acarreo en paralelo**

CPG: Carry Propagator Generator

Símbolo lógico

Ventaja: Rapidez

Característica: No es modular

**SUMADOR EN PARALELO DE VARIOS BITS Sumador con generación del acarreo en paralelo**

Símbolo lógico

**SUMADOR EN PARALELO DE VARIOS BITS Sumador con generación del acarreo en paralelo**

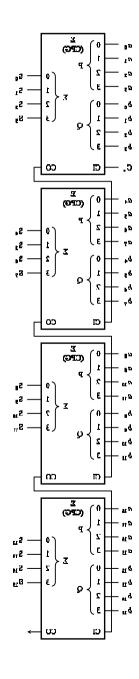

**SOLUCIONES INTERMEDIAS**

Solución lenta

Bloques funcionales con generación del acarreo en paralelo conectados con propagacion del acarreoen serie

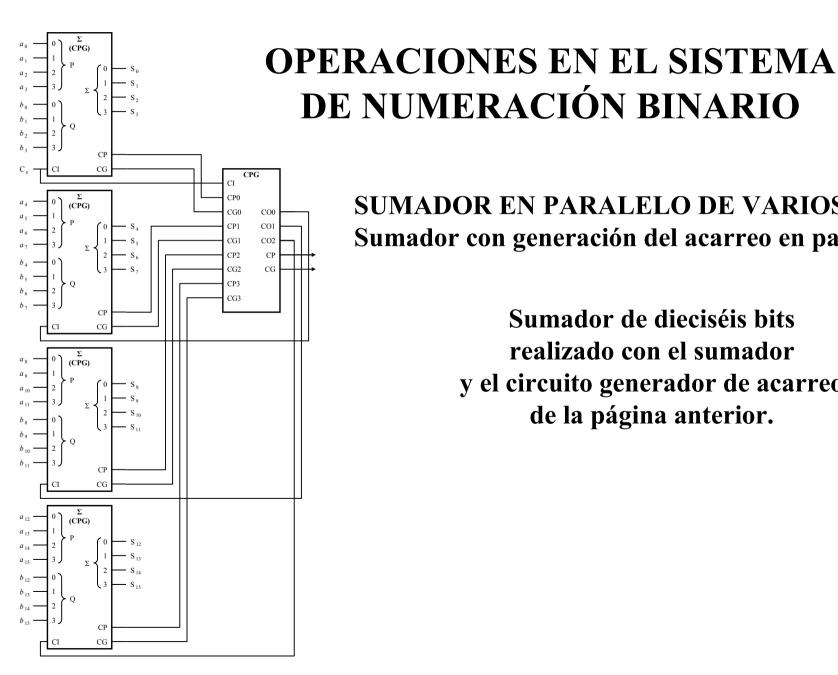

#### **SUMADOR EN PARALELO DE VARIOS BITS Sumador con generación del acarreo en paralelo**

Símbolo lógico de un sumador de cuatro bits con generación del acarreo en paralelo

### DE NUMERACIÓN BINARIO

SUMADOR EN PARALELO DE VARIOS BITS Sumador con generación del acarreo en paralelo

> Sumador de dieciséis bits realizado con el sumador y el circuito generador de acarreo de la página anterior.

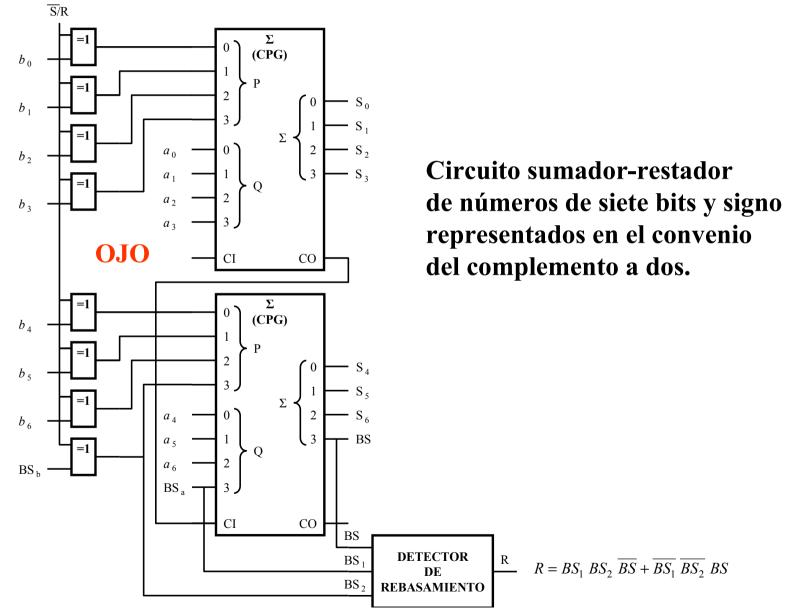

#### **RESTA BINARIA**

Representación de los números negativos:

- Valor absoluto y signo

- Complemento a dos

- Complemento a uno

- Binario desplazado

#### **COMPLEMENTO A DOS**

Ejemplo

$$- \frac{1 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0}{BS}$$

$$- 19 \equiv 1 \quad 0 \quad 1 \quad 0 \quad 1$$

Se comprueba que se obtiene el mismo resultado invirtiendo el número binario equivalente a 19 y sumándole la unidad.

#### **COMPLEMENTO A UNO**

$$-19_{10} \equiv 1 \quad 0 \quad 1 \quad 1 \quad 0 \quad 0$$

BINARIO DESPLAZADO (BINARY OFFSET)

| Exponent e decimal | Codificación en<br>binario desplazado |   |   | Binario natural en complemento a dos |   |   |   |   |

|--------------------|---------------------------------------|---|---|--------------------------------------|---|---|---|---|

| -8                 | 0                                     | 0 | 0 | 0                                    | 1 | 0 | 0 | 0 |

| -7                 | 0                                     | 0 | 0 | 1                                    | 1 | 0 | 0 | 1 |

| -6                 | 0                                     | 0 | 1 | 0                                    | 1 | 0 | 1 | 0 |

| -5                 | 0                                     | 0 | 1 | 1                                    | 1 | 0 | 1 | 1 |

| -4                 | 0                                     | 1 | 0 | 0                                    | 1 | 1 | 0 | 0 |

| -3                 | 0                                     | 1 | 0 | 1                                    | 1 | 1 | 0 | 1 |

| -2                 | 0                                     | 1 | 1 | 0                                    | 1 | 1 | 1 | 0 |

| -1                 | 0                                     | 1 | 1 | 1                                    | 1 | 1 | 1 | 1 |

| 0                  | 1                                     | 0 | 0 | 0                                    | 0 | 0 | 0 | 0 |

| 1                  | 1                                     | 0 | 0 | 1                                    | 0 | 0 | 0 | 1 |

| 2                  | 1                                     | 0 | 1 | 0                                    | 0 | 0 | 1 | 0 |

| 3                  | 1                                     | 0 | 1 | 1                                    | 0 | 0 | 1 | 1 |

| 4                  | 1                                     | 1 | 0 | 0                                    | 0 | 1 | 0 | 0 |

| 5                  | 1                                     | 1 | 0 | 1                                    | 0 | 1 | 0 | 1 |

| 6                  | 1                                     | 1 | 1 | 0                                    | 0 | 1 | 1 | 0 |

| 7                  | 1                                     | 1 | 1 | 1                                    | 0 | 1 | 1 | 1 |

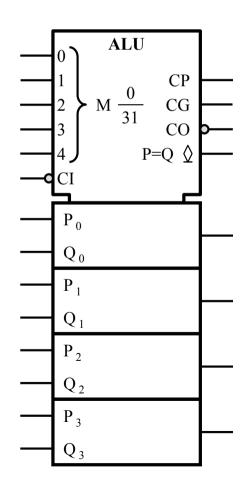

#### UNIDAD ARITMÉTICA Y LÓGICA

| Operaciones aritméticas         | Operaciones lógicas         |

|---------------------------------|-----------------------------|

| R = A                           | $R = \overline{A}$          |

| R = A + B                       | $R = \overline{A + B}$      |

| $R = \overline{A}B$             | $R = \overline{A}B$         |

| R = -1                          | R = 0                       |

| $R = A MAS A\overline{B}$       | $R = \overline{AB}$         |

| $R = (A + B) MAS A\overline{B}$ | $R = \overline{B}$          |

| R = A MENOS B MENOS 1           | $R = A \oplus B$            |

| $R = A\overline{B} MENOS1$      | $R = A\overline{B}$         |

| R = A MAS AB                    | $R = \overline{A} + B$      |

| R = A MAS B                     | $R = \overline{A \oplus B}$ |

| $R = (A + \overline{B}) MAS AB$ | R = B                       |

| R = AB MENOS 1                  | R = AB                      |

| R = A MAS A desplaz.            | R = 1                       |

| R = (A + B) MAS A               | $R = A + \overline{B}$      |

| $R = (A + \overline{B}) MAS A$  | R = A + B                   |

| R = A  MENOS  1                 | R = A                       |

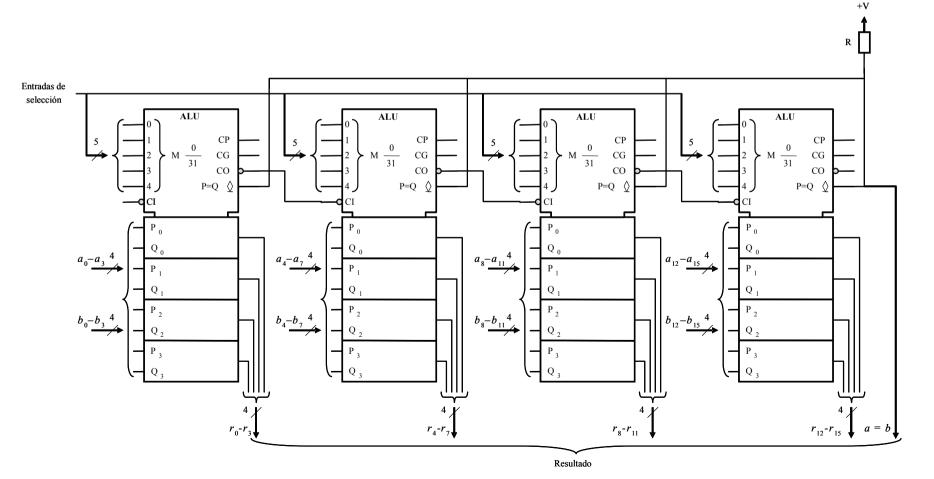

#### UNIDAD ARITMÉTICA CON PROPAGACIÓN DEL ACARREO EN SERIE

## OPERACIONES EN EL SISTEMA DE NUMERACIÓN BINARIO UNIDAD ARITMÉTICA CON PROPAGACIÓN DEL ACARREO EN

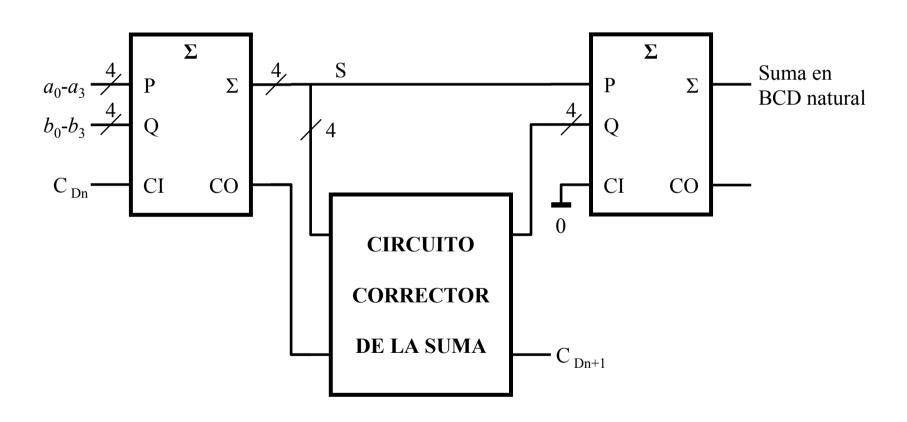

#### SUMA EN BCD NATURAL

$$a = 24_{10} \equiv (0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 0 \ 0)_{\text{BCD natural}}$$

$b = 17_{10} \equiv (0 \ 0 \ 0 \ 1 \ 0 \ 1 \ 1)_{\text{BCD natural}}$

#### SUMA EN BCD NATURAL

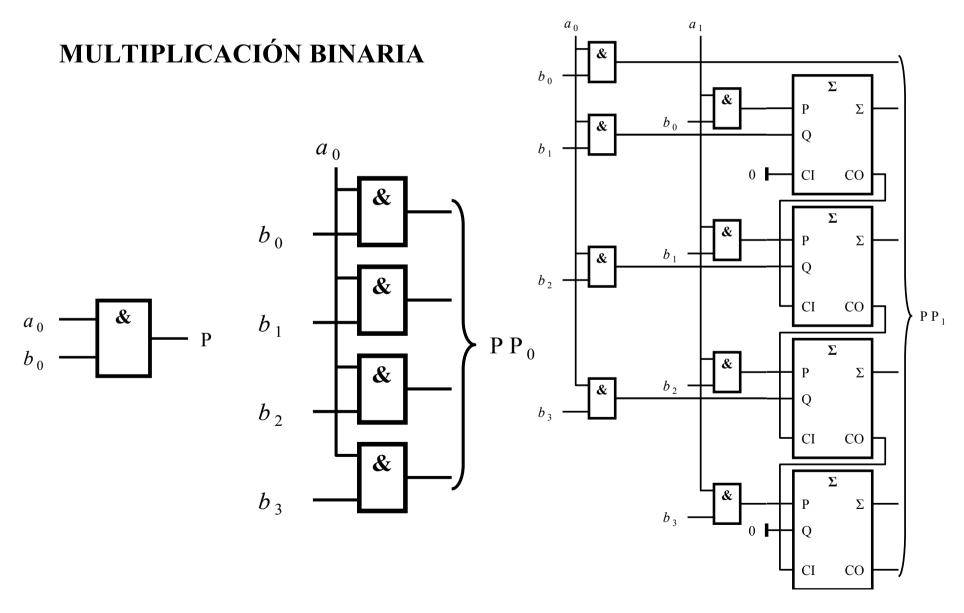

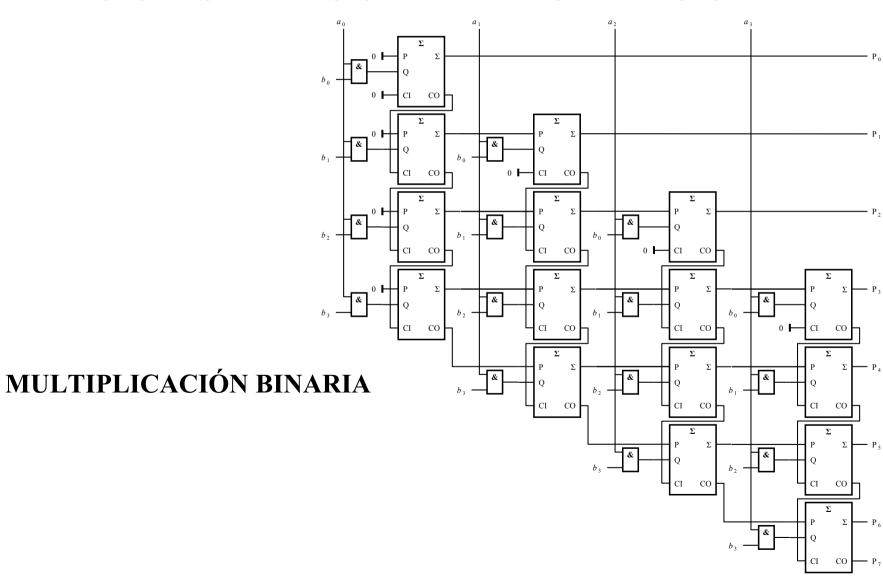

#### ALGORITMO DE LA SUMA EN BCD NATURAL