# ELECTRÓNICA DIGITAL Tema 13

**UNIDADES DE MEMORIA DIGITALES (PARTE 2)**

Enrique Mandado Pérez

#### MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA ALEATORIA

#### MEMORIAS DE ACCESO ALEATORIO

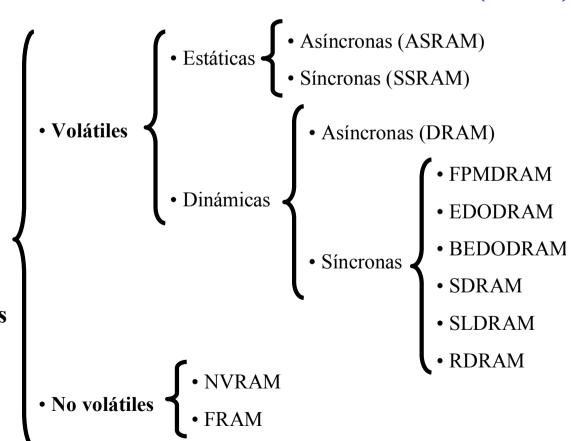

Clasificación de las memorias de acceso aleatorio

Según la volatilidad

Pasivas

Volátiles

No volátiles

Según la forma de realizar las operaciones de escritura y lectura

Escritura y lectura simultáneas

Escritura y lectura no simultáneas

Acceso múltiple

#### ACTIVAS (READ/WRITE)

El tiempo que tarda en realizarse una operación de escritura y una de lectura es del mismo orden de magnitud. Pueden ser volátiles o no volátiles.

#### PASIVAS (READ ONLY)

Tardan mucho más en ser escritas que en ser leídas. No son volátiles.

#### **MEMORIAS ACTIVAS**

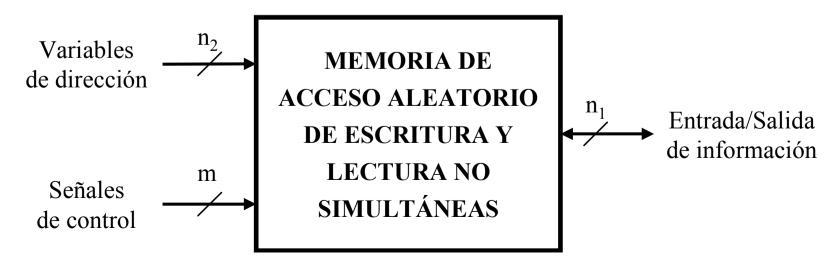

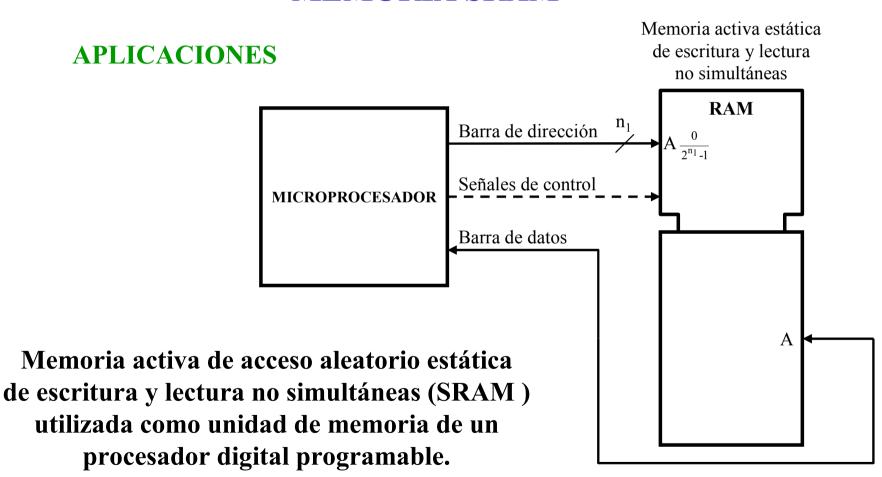

Se suelen denominar memorias de escritura/lectura (Read/Write) y se les llama RAM cuando son de escritura y lectura no simultáneas.

#### Se pueden implementar:

- Con biestables activados por niveles Se denominan estáticas (SRAM)

- Con condensadores Se denominan dinámicas (DRAM)

#### MEMORIAS DE ACCESO ALEATORIO ACTIVAS DE ESCRITURA Y LECTURA NO SIMULTANEAS (RAM)

Clasificación

según la volatilidad

de las memorias

de acceso aleatorio

activas de escritura y

lectura no simultáneas

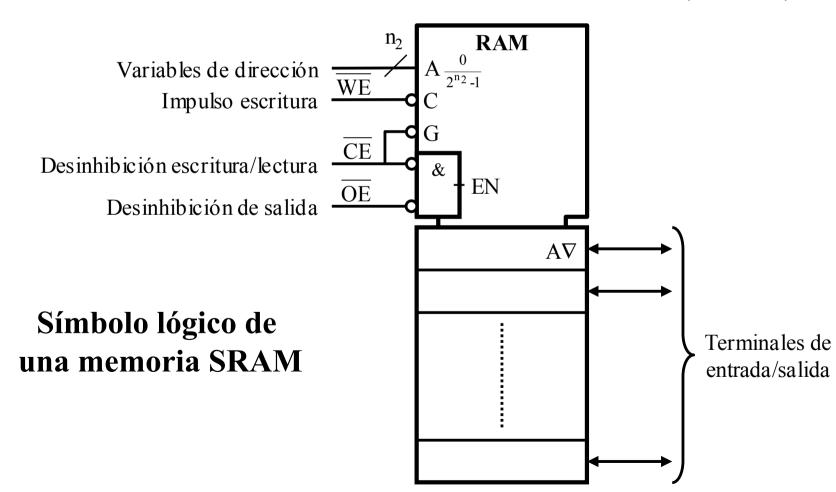

### MEMORIAS RAM ACTIVAS ESTÁTICAS DE ESCRITURA Y LECTURA NO SIMULTÁNEAS (SRAM)

Se caracterizan porque solo se puede seleccionar en cada instante una posición para escribir en ella o leer la información que contiene. Se pueden clasificar en dos grandes tipos:

- Memorias SRAM asíncronas (ASRAM).

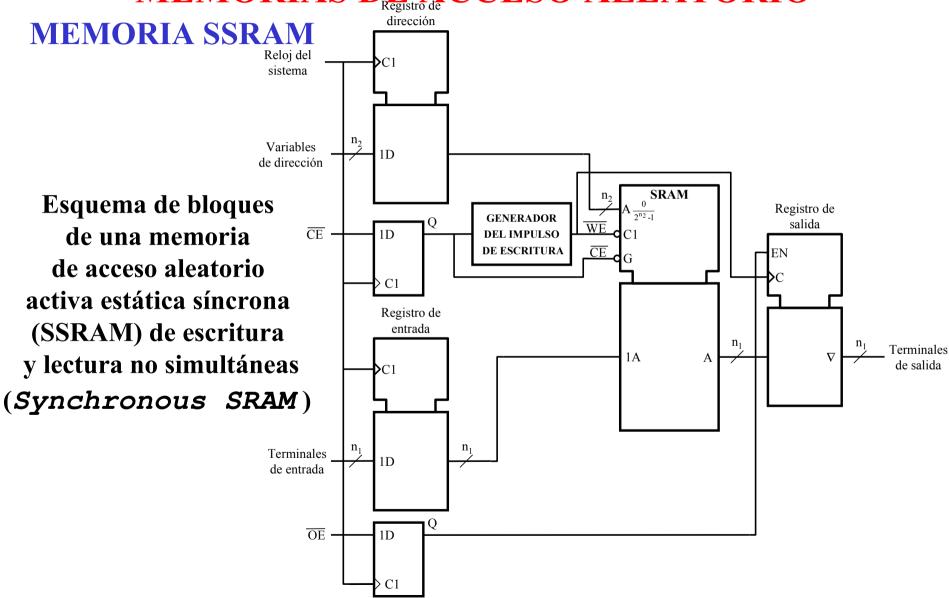

- Memorias SRAM síncronas (SSRAM).

#### MEMORIAS RAM ACTIVAS ESTÁTICAS DE ESCRITURA Y LECTURA NO SIMULTÁNEAS (SRAM)

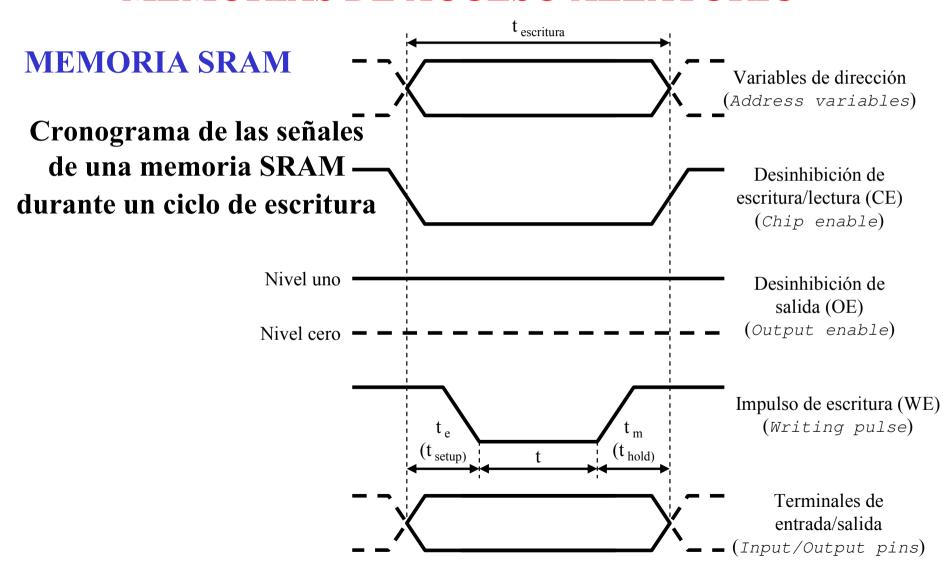

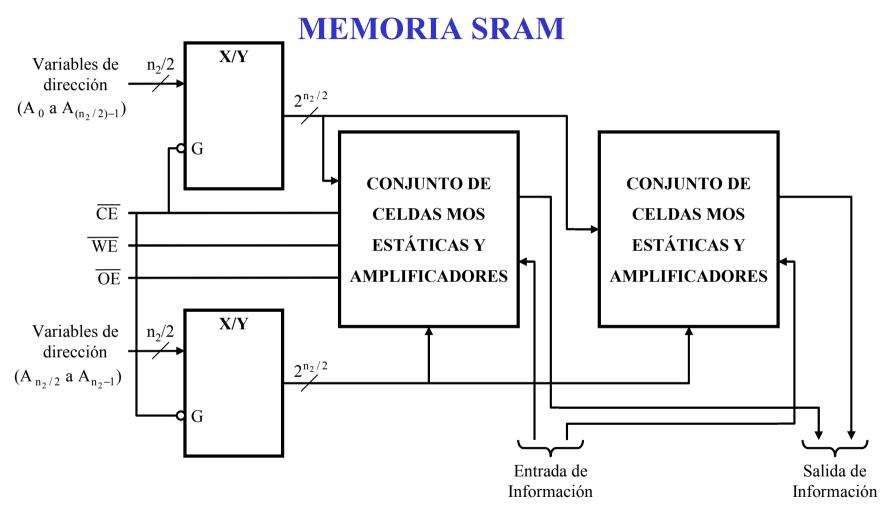

MEMORIA SRAM

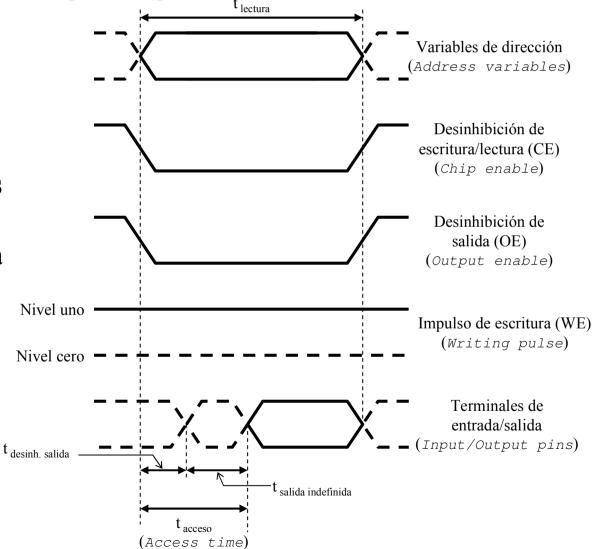

t<sub>lectura</sub>

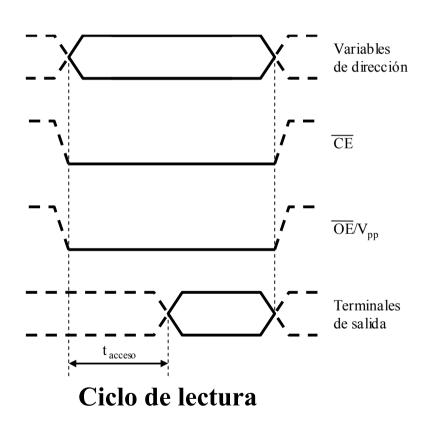

Cronograma de las señales de una memoria SRAM durante un ciclo de lectura

#### **MEMORIA SRAM**

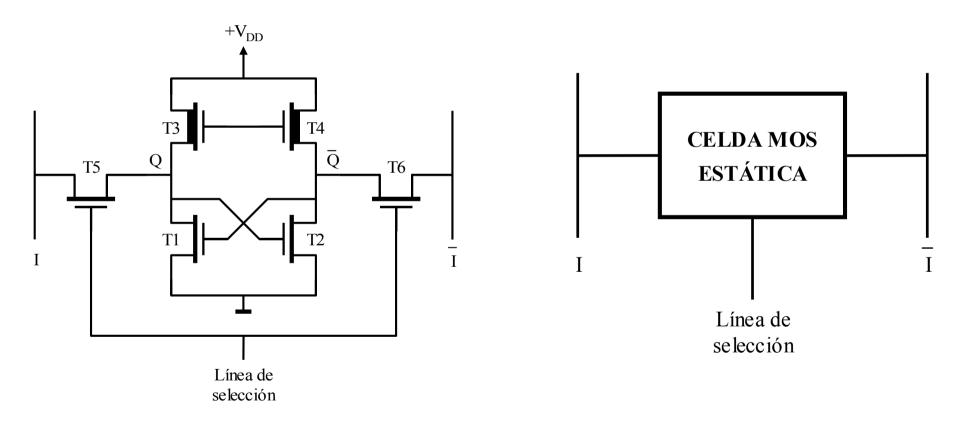

Esquema y bloque funcional de una memoria SRAM de tecnología MOS de canal N

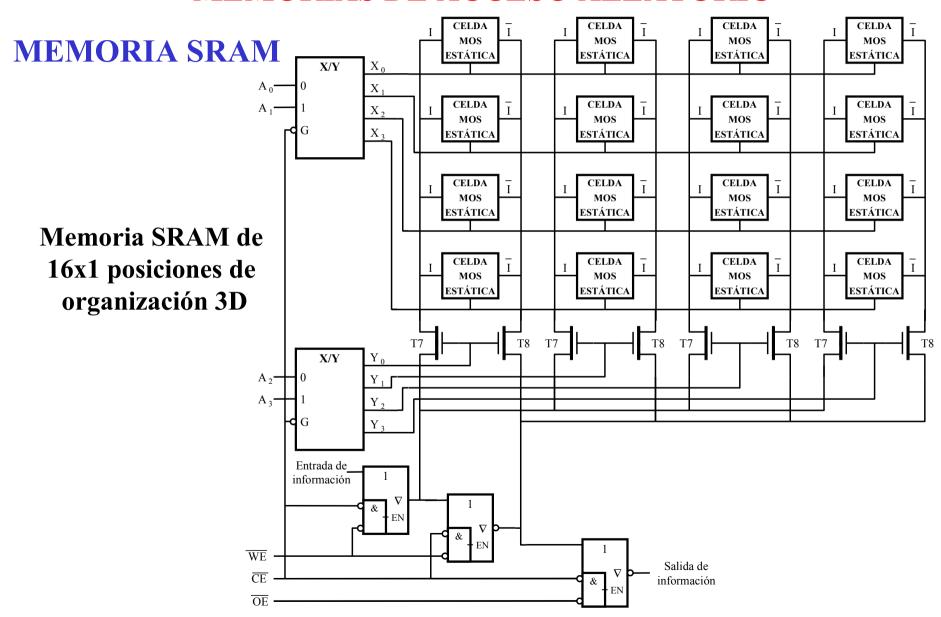

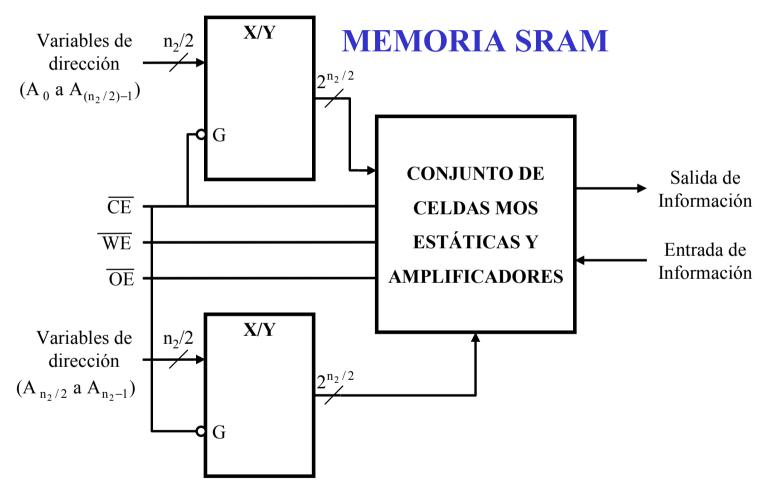

Esquema de bloques de una memoria de acceso aleatorio estática de  $2n^2$  posiciones de un bit

Esquema de bloques de una memoria activa de acceso aleatorio estática de  $2^{n^2}$  posiciones de dos bits cada una, con organización 3D

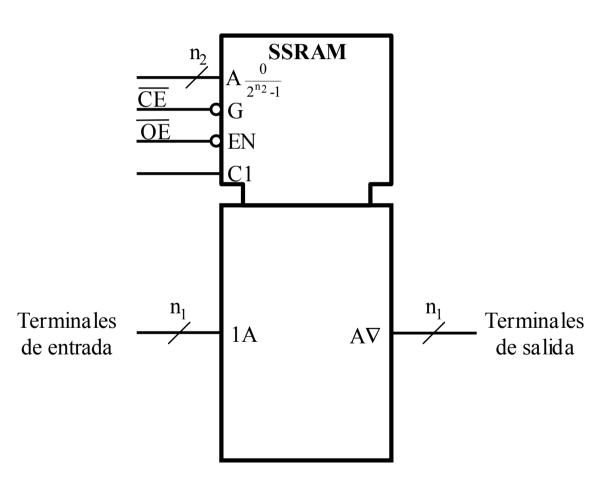

Símbolo lógico de una memoria de acceso aleatorio activa estática síncrona (SSRAM) de escritura y lectura no simultáneas

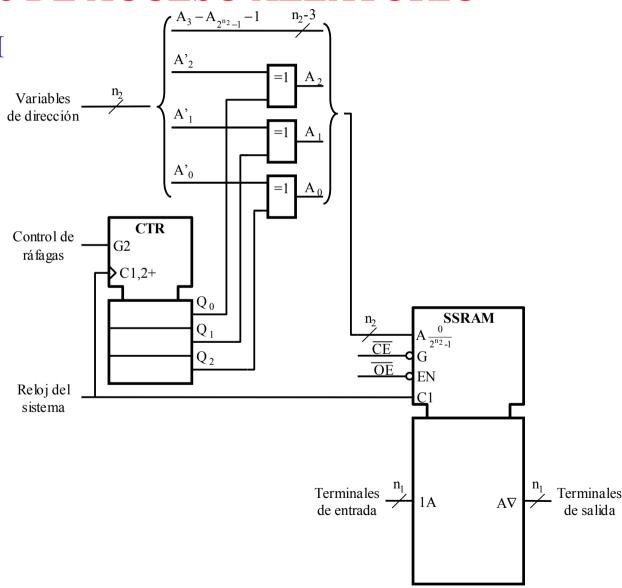

#### **MEMORIA BSSRAM**

Esquema de bloques

de una memoria

de acceso aleatorio

activa estática síncrona

de ráfagas (BSSRAM)

de escritura y lectura

no simultáneas

(Burst Synchronous

SRAM)

# MEMORIAS DE ACCESO ALEATORIO MEMORIA DE ACCESO ALEATORIO DINÁMICA DE LECTURA Y ESCRITURA NO SIMULTÁNEAS (DRAM)

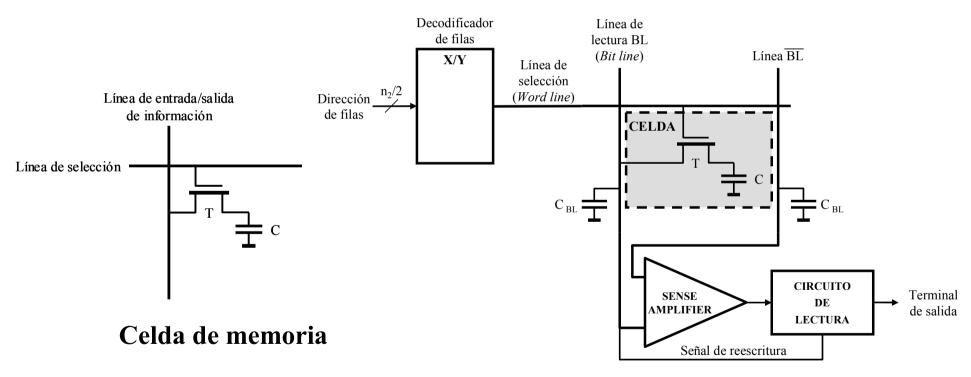

Esquema de bloques del circuito de lectura y regrabado.

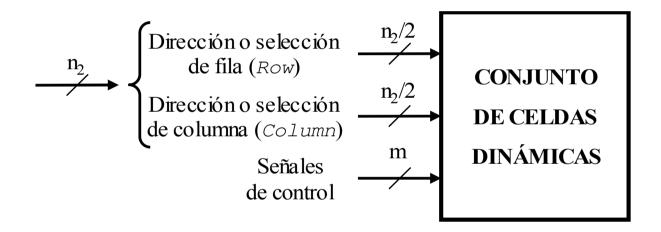

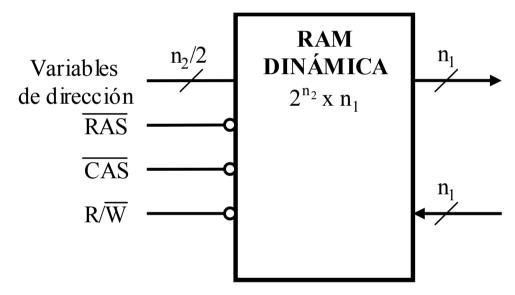

Bloque funcional básico de una memoria de acceso aleatorio dinámica de escritura y lectura no simultáneas (DRAM)

**MEMORIA DRAM**

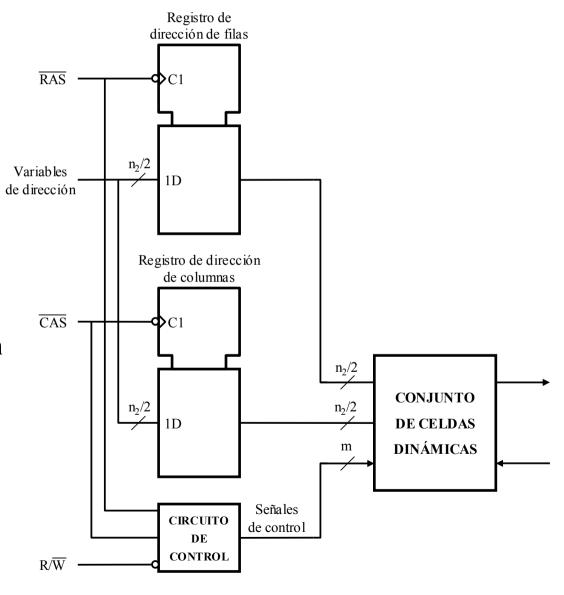

Esquema de bloques de una memoria de acceso aleatorio dinámica de escritura y lectura no simultáneas con registros temporales de memorización de la dirección

Símbolo lógico de una memoria de acceso aleatorio dinámica de escritura y lectura no simultáneas con registros temporales de memorización de la dirección

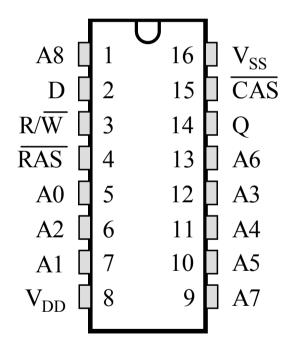

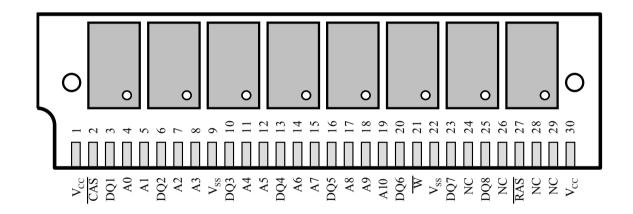

Encapsulado de la memoria DRAM TMS 4256 de 256K1

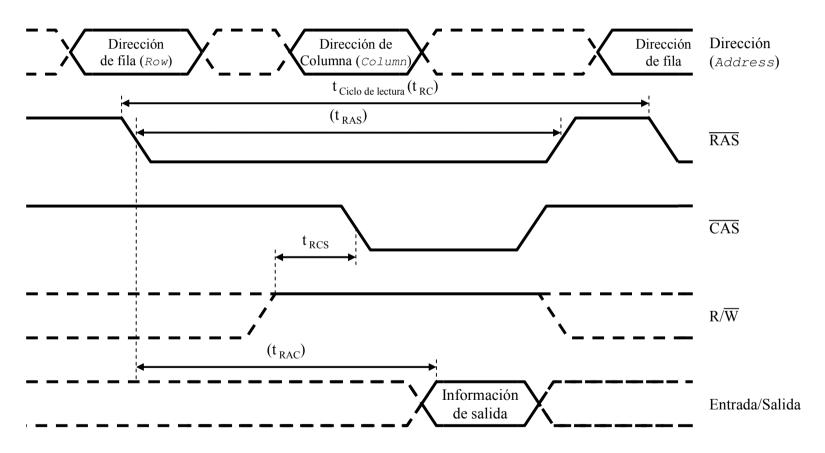

Cronograma de las señales de una memoria de acceso aleatorio dinámica de escritura y lectura no simultáneas durante un ciclo de lectura

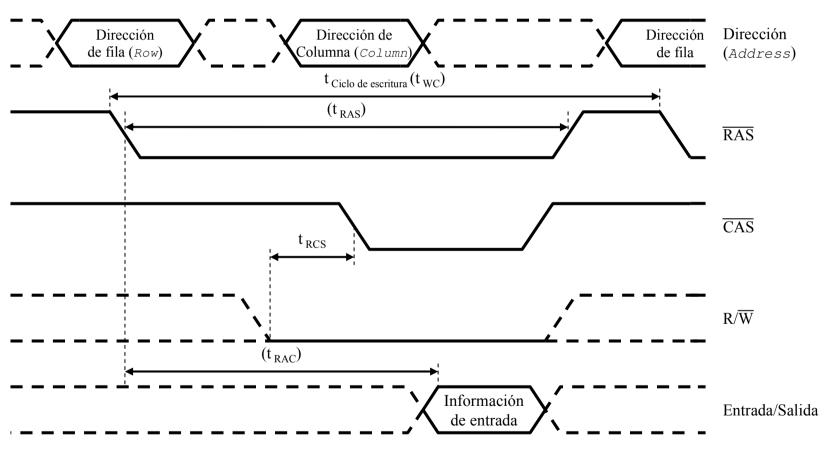

Cronograma de las señales de una memoria de acceso aleatorio dinámica de escritura y lectura no simultáneas durante un ciclo de escritura

Memoria de acceso aleatorio dinámica de escritura y lectura no simultáneas (DRAM) con circuito controlador de regrabado (Refreshing)

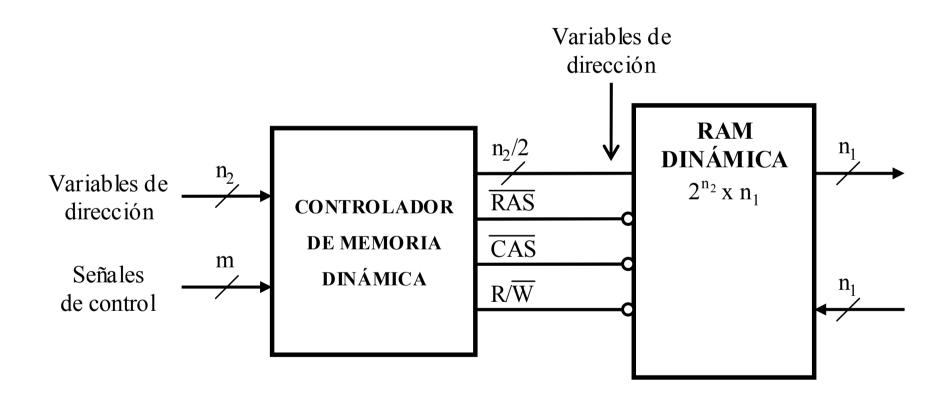

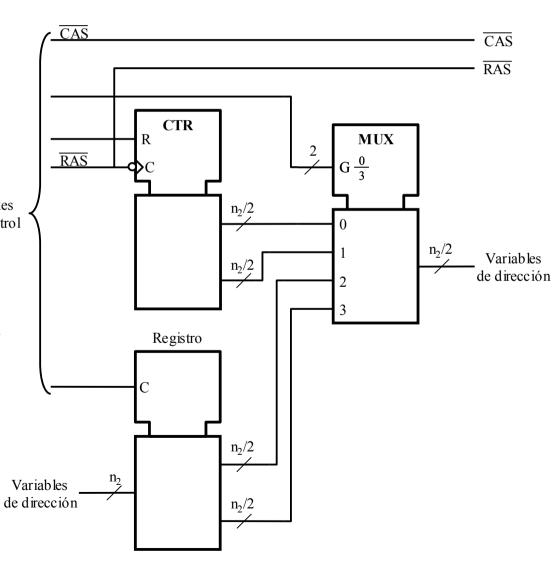

Esquema de bloques básico

de un controlador de una Señales

memoria de acceso aleatorio de control

dinámica de escritura y lectura

no simultáneas (DRAM)

sin generador de señales de control

(Timing controller)

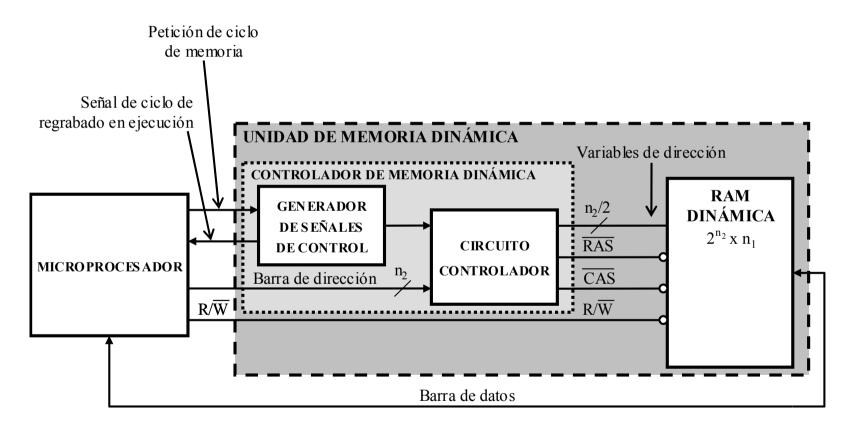

Unidad de memoria de acceso aleatorio dinámica de escritura y lectura no simultáneas (DRAM) acoplada a un microprocesador

#### MEMORIAS DE ACCESO ALEATORIO MEMORIA DRAM AVANZADAS

• Estáticas • Asíncronas (ASRAM)

• Volátiles

• Asíncronas (SSRAM)

• Asíncronas (DRAM)

• FPMDRAM

• EDODRAM

• BEDODRAM

• SDRAM

• SLDRAM Clasificación según la volatilidad de las memorias de acceso aleatorio activas de escritura y lectura no simultáneas

#### MEMORIAS DE ACCESO ALEATORIO MEMORIA DRAM AVANZADAS FPMDRAM

Se basan en que la mayoría de los programas que se ejecutan en los computadores de aplicación general acceden a direcciones de la memoria que están en la misma página y la parte alta de la dirección permanece constante. Si dicha parte se aplica a la dirección de las filas se puede mantener la entrada en un nivel constante y aplicar flancos de bajada sucesivos a la entrada. De esa forma la precarga, descrita anteriormente, se hace una sola vez y se disminuye el tiempo de acceso.

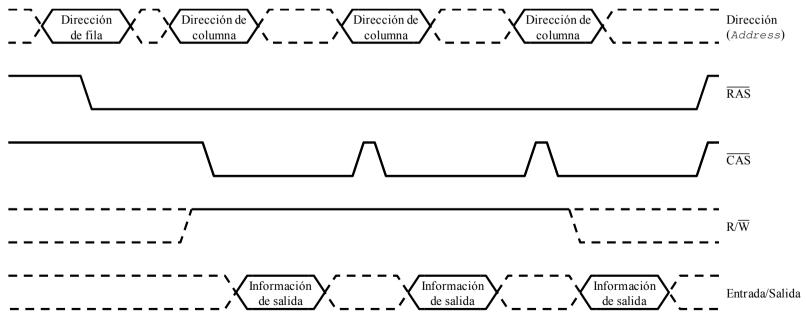

Cronograma de las señales de una memoria FPMDRAM (Fast Page Mode DRAM) durante un ciclo de lectura

Módulo SIMM (Single-In –Line Module) de una memoria DRAM

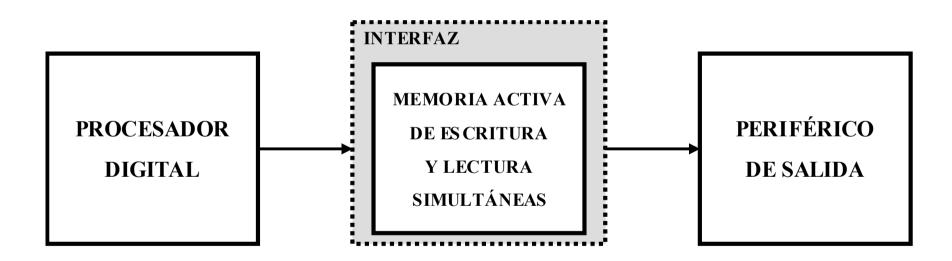

#### MEMORIAS DE ACCESO ALEATORIO MEMORIA ACTIVA RAM DE ESCRITURA Y LECTURA SIMULTÁNEAS

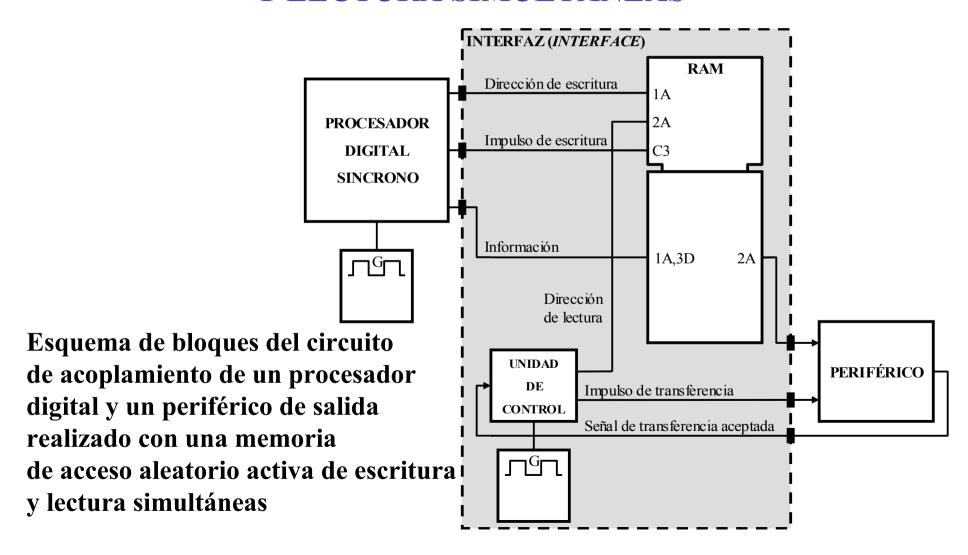

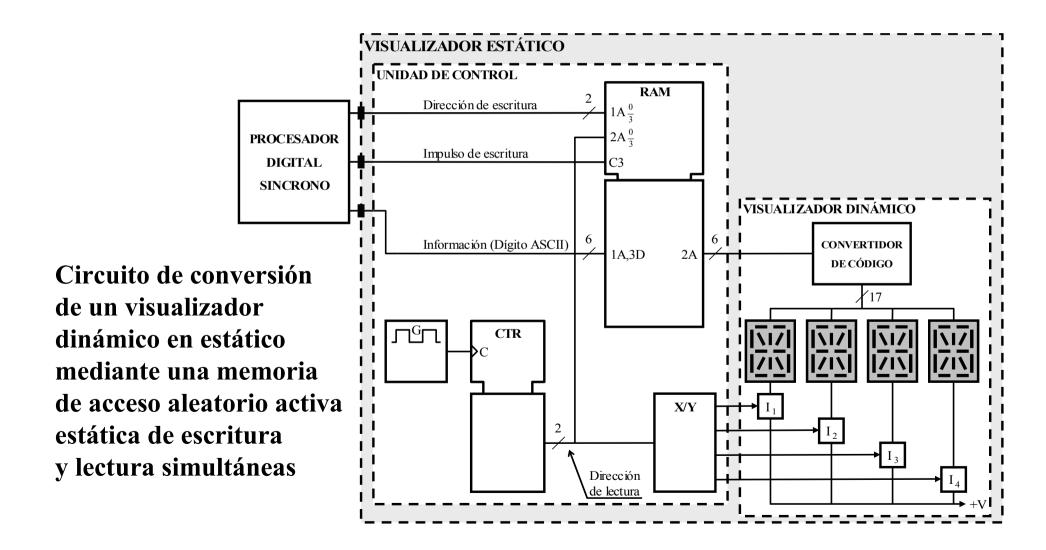

Memoria de acceso aleatorio activa de escritura y lectura simultáneas como interfaz entre un procesador y un periférico de salida

## MEMORIAS DE ACCESO ALEATORIO MEMORIA ACTIVA RAM DE ESCRITURA Y LECTURA SIMULTÁNEAS

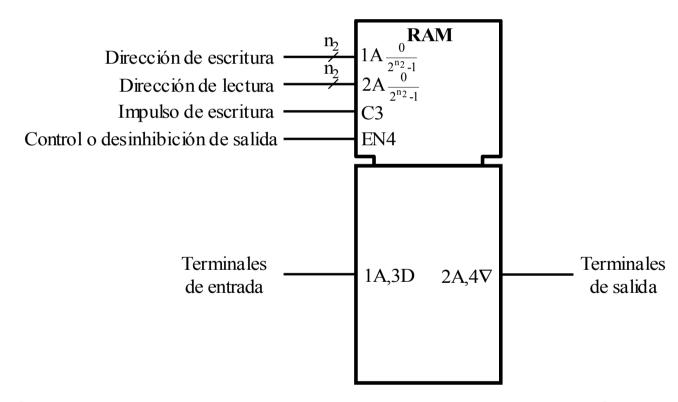

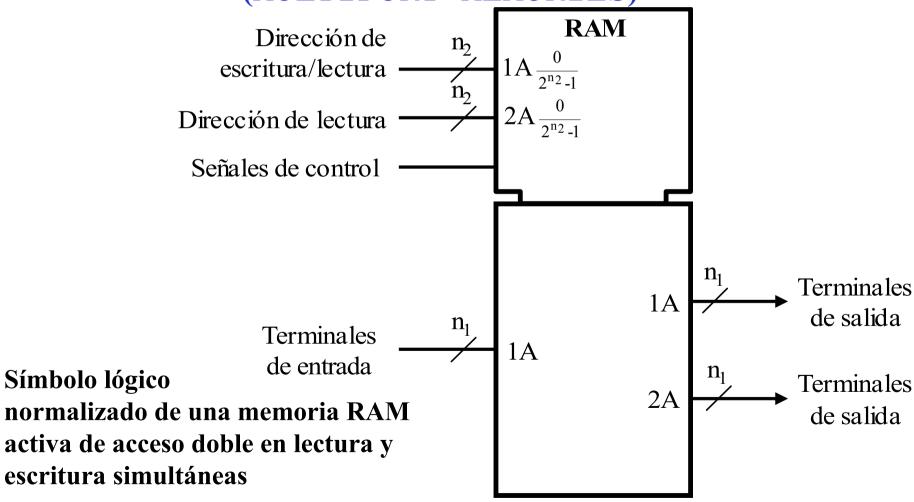

Símbolo lógico de una memoria de acceso aleatorio activa estática de escritura y lectura simultáneas

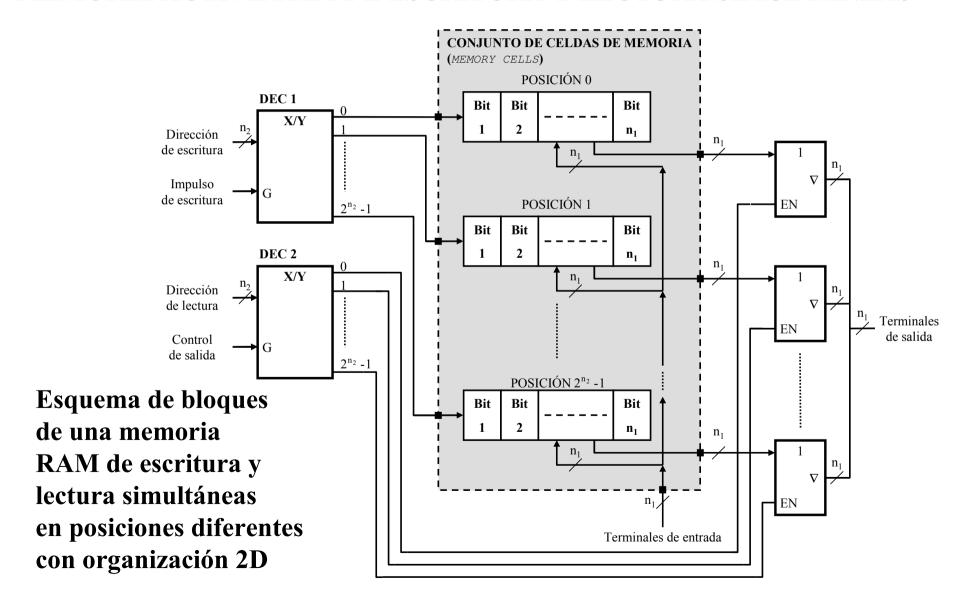

#### MEMORIAS DE ACCESO ALEATORIO MEMORIA ACTIVA RAM DE ESCRITURA Y LECTURA SIMULTÁNEAS

#### MEMORIAS DE ACCESO ALEATORIO MEMORIA ACTIVA RAM DE ESCRITURA Y LECTURA SIMULTÁNEAS

### MEMORIAS DE ACCESO ALEATORIO MEMORIA ACTIVA RAM DE ESCRITURA Y LECTURA SIMULTÁNEAS

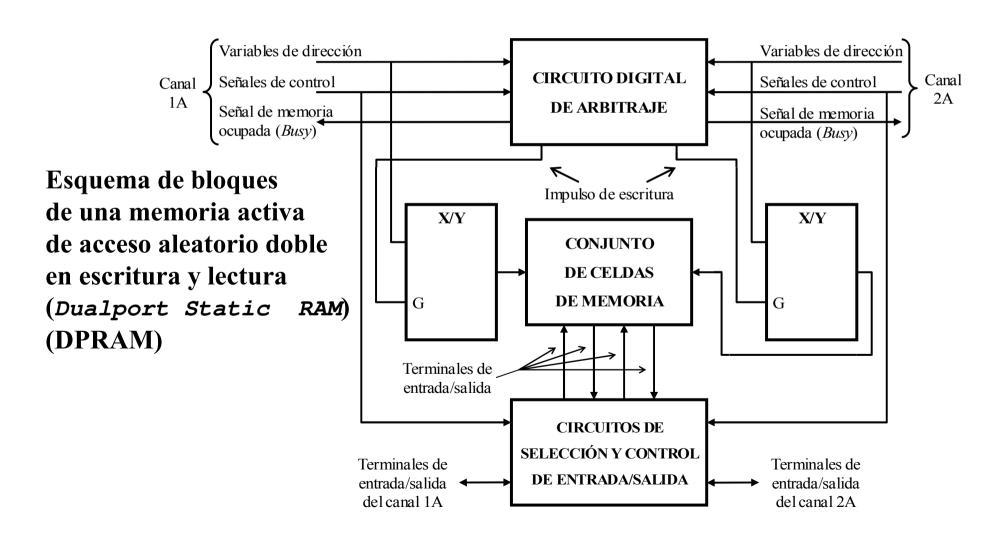

#### MEMORIA RAM DE ACCESO MÚLTIPLE

(MULTIPORT MEMORIES)

### MEMORIAS DE ACCESO ALEATORIO MEMORIA RAM DE ACCESO MÚLTIPLE

# MEMORIAS DE ACCESO ALEATORIO MEMORIA RAM DE ACCESO MÚLTIPLE

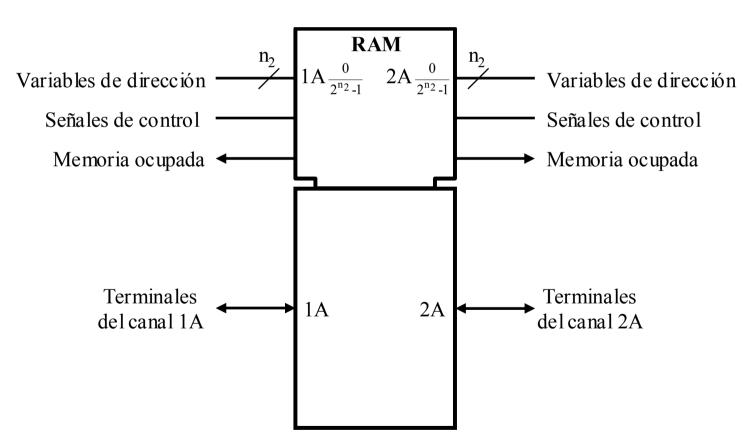

Símbolo lógico de una memoria DPRAM

# MEMORIAS DE ACCESO ALEATORIO MEMORIA RAM DE ACCESO MÚLTIPLE

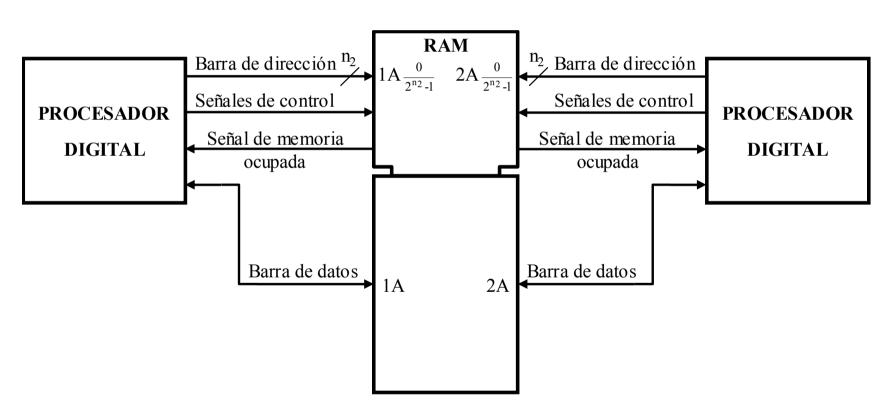

Utilización de una memoria DPRAM para acoplar dos procesadores digitales

#### MEMORIAS DE ACCESO ALEATORIO MEMORIA RAM DE ACCESO MÚLTIPLE

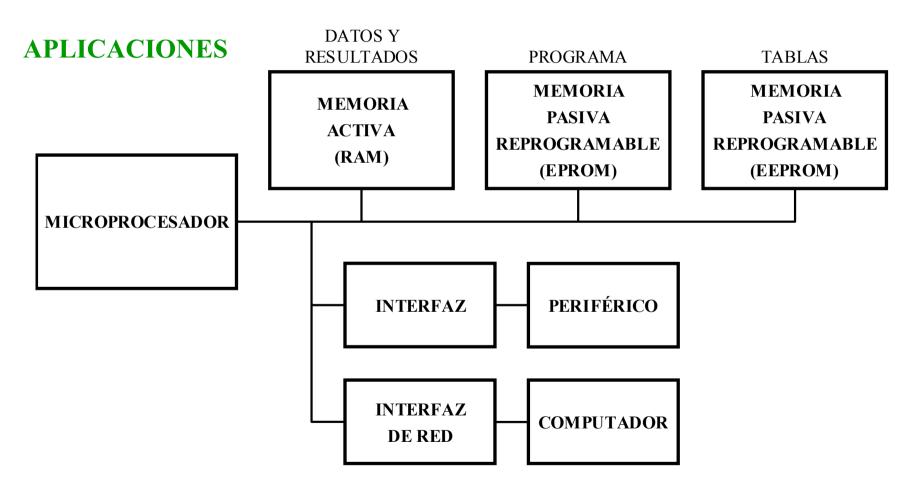

#### **APLICACIONES**

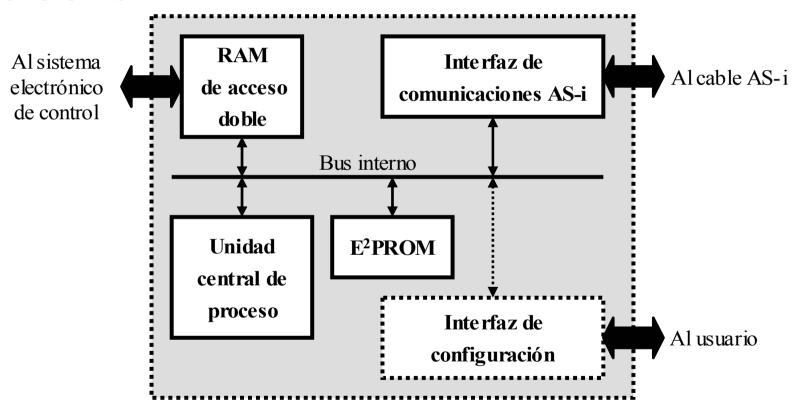

Esquema de bloques del procesador de comunicaciones principal de una red de comunicaciones AS-i que utiliza una memoria DPRAM

### MEMORIAS DE ACCESO ALEATORIO MEMORIA RAM DE ACCESO MÚLTIPLE

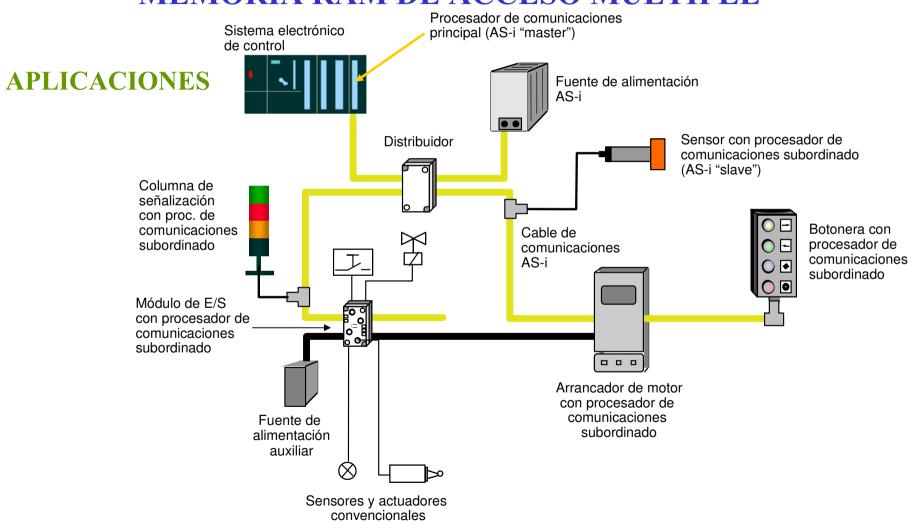

Ejemplo real de red AS-i (Cortesía de Siemens).

# MEMORIAS DE ACCESO ALEATORIO MEMORIA RAM DE ACCESO MÚLTIPLE

#### **APLICACIONES**

Circuito integrado AS-i "A2SI": a) Diagrama de bloques. b) Placa de circuito impreso para el diseño de subordinados AS-i. (Cortesía de ZMD y Bihl&Wiedemann) []

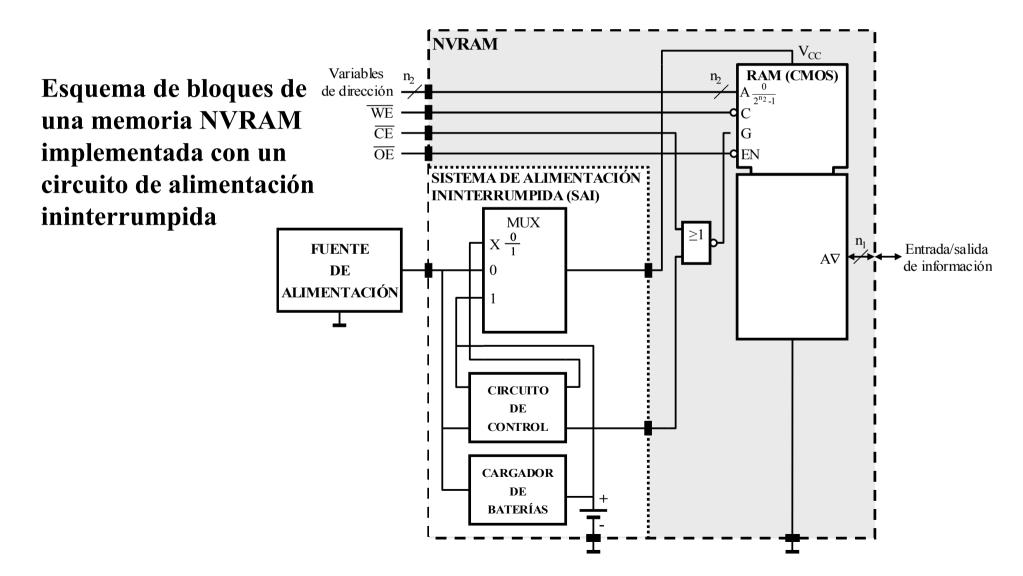

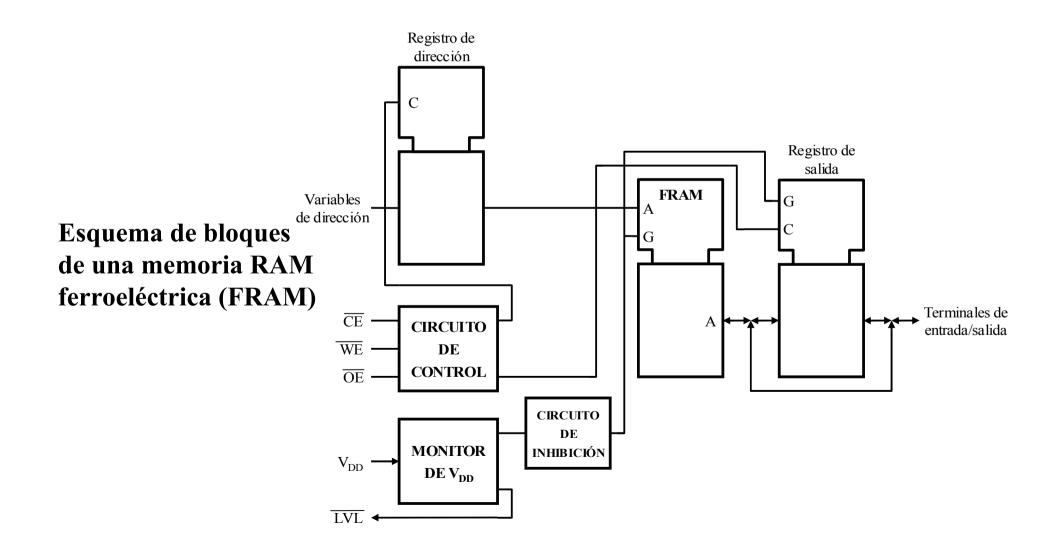

#### MEMORIAS DE ACCESO ALEATORIO MEMORIAS RAM ACTIVAS NO VOLÁTILES (NVRAM)

#### MEMORIAS DE ACCESO ALEATORIO MEMORIAS RAM ACTIVAS NO VOLÁTILES

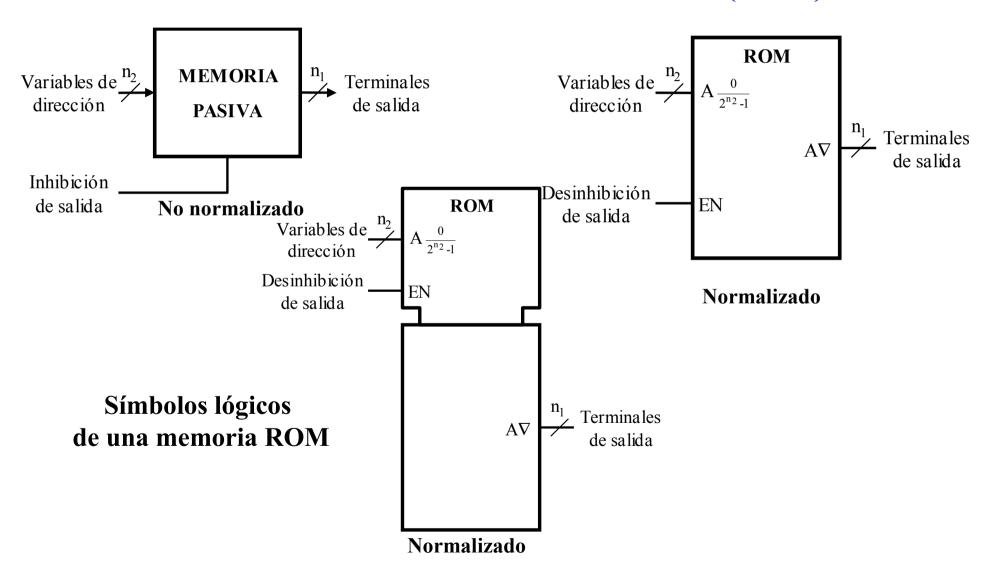

# MEMORIAS DE ACCESO ALEATORIO MEMORIAS PASIVAS

Memorias de acceso aleatorio que están implementadas con elementos de memoria no volátiles cuyo tiempo de lectura es mucho menor que el de escritura. Reciben la denominación general de memorias ROM (Read Only Memories) y se caracterizan por:

- Tienen tiempos de escritura y lectura muy diferentes que dependen del principio físico en el que se basa el elemento de memoria utilizado.

- No son volátiles lo que las hace idóneas para el almacenamiento de una parte o de todas las instrucciones de los procesadores digitales secuenciales síncronos programables conocidos como computadores

- Su celda básica es sencilla porque sólo contiene uno o dos elementos dispositivos semiconductores.

#### MEMORIAS DE ACCESO ALEATORIO

#### **MEMORIAS PASIVAS**

Clasificación de las memorias de acceso aleatorio pasivas

• Totalmente pasivas: • ROM

Pasivas programables

OTP EPROM

- Pasivas reprogramables

Borrables mediante rayos ultravioleta (EPROM)

Borrables eléctricamente por efecto túnel (EEPROM)

FLASH

#### MEMORIAS DE ACCESO ALEATORIO MEMORIAS PASIVAS

#### **APLICACIONES**

- Implementación de generadores de caracteres (Character generators) que son convertidores de código, como por ejemplo del código ASCII al de 5 por 7 puntos

- Implementación del circuito combinacional de los sistemas secuenciales síncronos programables.

- Almacenamiento de todas las instrucciones, o de una parte de ellas, de los computadores de arquitectura Princeton (Von Neumann) o Harvard.

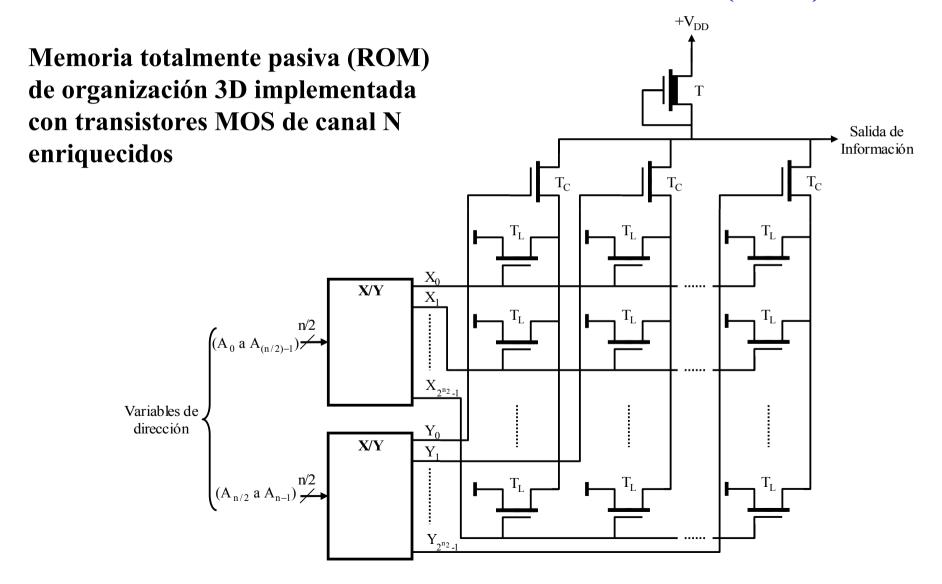

### MEMORIAS DE ACCESO ALEATORIO MEMORIAS TOTALMENTE PASIVAS (ROM)

Son conocidas simplemente como ROM (acrónimo de Read Only Memories). Son memorias de acceso aleatorio que nunca pueden ser escritas por el usuario. Al colocarlas en un sistema digital sólo pueden ser leídas. La grabación o escritura la realiza el fabricante durante el proceso de fabricación. Debido a que dicho proceso se lleva acabo mediante la utilización de una secuencia de

máscaras, estas memorias suelen recibir la denominación

de memorias programables por máscara (Mask

Programmable ROM)

#### MEMORIAS DE ACCESO ALEATORIO MEMORIAS TOTALMENTE PASIVAS (ROM)

#### MEMORIAS DE ACCESO ALEATORIO MEMORIAS TOTALMENTE PASIVAS (ROM)

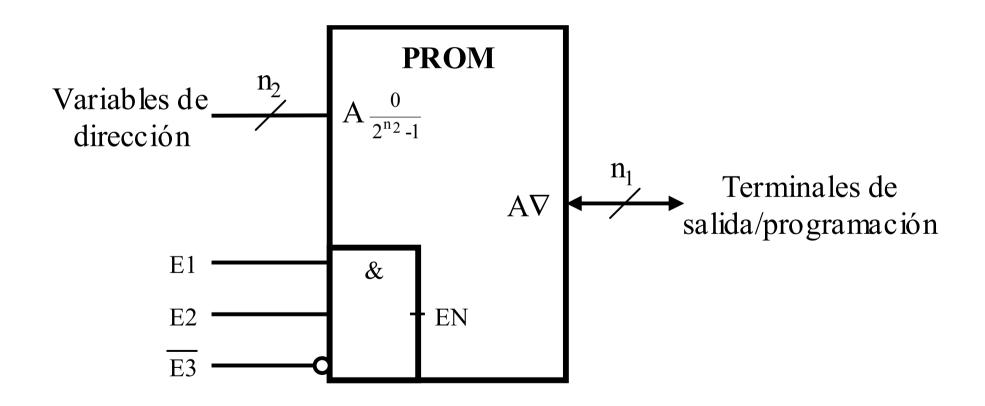

Son memorias de acceso aleatorio cuyo contenido puede ser escrito por el usuario una sola vez. Por ello se llaman PROM (*Programmable Read Only Memories*)

Las de uso más extendido se implementaron en tecnología TTL y utilizaron la celda de memoria formada por un transistor bipolar y un diodo.

Han dejado de utilizarse porque han sido sustituidas con ventaja por las memorias reprogramables implementadas con transistores MOS.

También se pueden considerar PROM las memorias OTP EPROM.

Símbolo lógico de una memoria PROM con salida de tres estados

Son memorias de acceso aleatorio cuyo contenido puede ser escrito por el usuario varias veces. Se diferencian de las memorias de acceso aleatorio activas en que el tiempo de escritura es en general mayor que el de lectura. Hay tres tipos de memorias RPROM:

- EPROM

- EEPROM

- FLASH

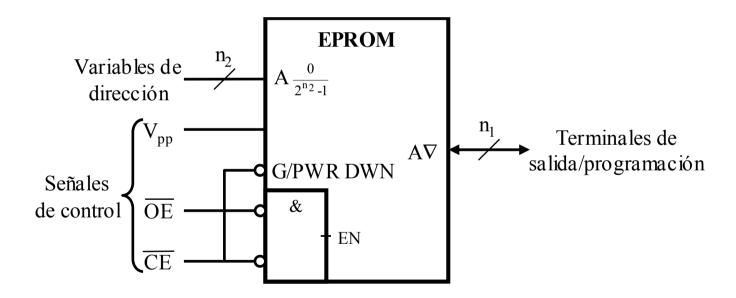

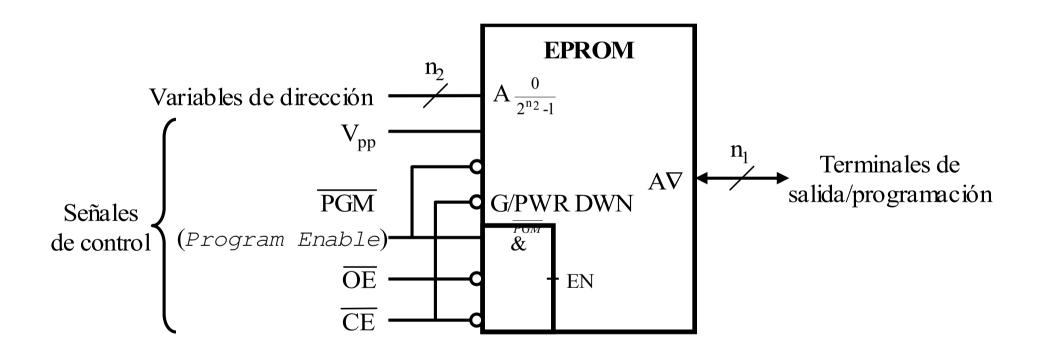

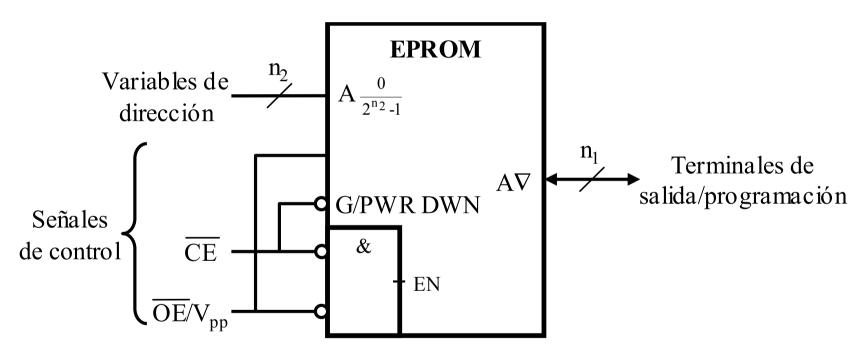

Las memorias pasivas reprogramables, conocidas como EPROM (*Erasable Programmable Read Only Memories*) se graban mediante impulsos eléctricos cuyo nivel de tensión es mayor que el utilizado durante la operación del circuito.

Utilizan en su implementación los transistores MOS de puerta flotante borrables con rayos ultravioleta La grabación consiste en inyectar portadores de carga en dicha puerta, mediante impulsos eléctricos. El borrado se realiza mediante rayos ultravioleta, para lo cual el circuito se encapsula de forma que queda situado debajo de una zona (ventana) transparente que permite el paso de los citados rayos, y por ello algunos fabricantes las denominan UVEPROM.

Las memorias EPROM que carecen de la citada ventana solo se pueden programar una vez y por ello se denominan OTP (One Time Programmable) EPROM.

Símbolo lógico de una memoria de acceso aleatorio pasiva reprogramable EPROM con terminal independiente para la tensión de grabación ( $V_{PP}$ ) e impulso de grabación a través del terminal de desinhibición CE).

Símbolo lógico de una memoria de acceso aleatorio pasiva reprogramable EPROM con terminal independiente para la tensión de grabación  $(V_{PP})$  y para el impulso de grabación  $\overline{PGM}$

Símbolo lógico de una memoria de acceso aleatorio pasiva reprogramable EPROM con terminal único de desinhibición de salida y tensión de grabación (OE/ Vpp)

|                                                          | Señales de control |                                 | Variables<br>de<br>dirección |         | Tensión de<br>alimentación | Terminales<br>salida/programación |

|----------------------------------------------------------|--------------------|---------------------------------|------------------------------|---------|----------------------------|-----------------------------------|

| Modo de operación                                        | CE                 | $\overline{\mathbf{OE}}/V_{PP}$ | $A_k$                        | $A_{i}$ | $\mathbf{V}_{\mathbf{CC}}$ | $D_{n_1-1} - D_0$                 |

| Lectura (Read)                                           | 0                  | 0                               | X                            | X       | 5V                         | Información memoria               |

| Inhibición de salida (Output enable)                     | 0                  | 1                               | X                            | X       | 5V                         | Tercer estado                     |

| Mínimo consumo (Standby)                                 | 1                  | X                               | X                            | X       | 5V                         | Tercer estado                     |

| Programación (Programming)                               | 0                  | $V_{PP}$                        | X                            | X       | $V_{Prog.}$                | Información externa               |

| Verificación (Test)                                      | 0                  | 0                               | X                            | X       | $V_{Prog.}$                | Información memoria               |

| Inhibición de programación ( <i>Programming enable</i> ) | 1                  | $V_{PP}$                        | X                            | X       | $V_{Prog.}$                | Tercer estado                     |

| Identificación inteligente                               |                    |                                 |                              |         |                            |                                   |

| (Electronic signature)                                   |                    |                                 |                              |         |                            |                                   |

| - Fabricante ( <i>Manufacturer code</i> )                | 0                  | 0                               | $V_{id}$                     | 0       | 5V                         | Cod. Fabricante                   |

| - Dispositivo (Device code)                              | 0                  | 0                               | $V_{id}$                     | 1       | 5V                         | Cod. Circuito                     |

#### MEMORIAS DE ACCESO ALEATORIO

#### MEMORIAS PASIVAS REPROGRAMABLES EPROM

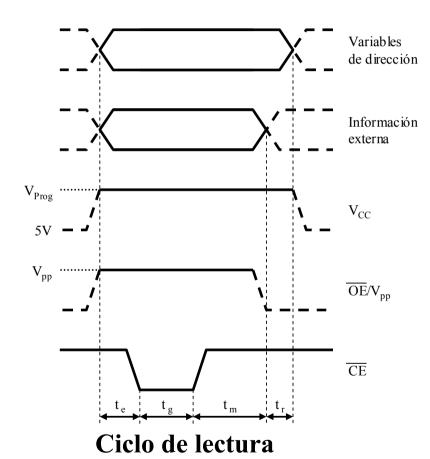

Cronograma de las señales aplicadas a la memoria pasiva reprogramable EPROM de la diapositiva 54

#### MEMORIAS DE ACCESO ALEATORIO

#### MEMORIAS PASIVAS REPROGRAMABLES EPROM

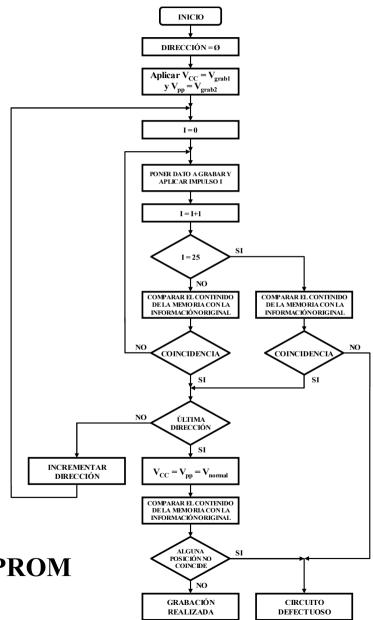

Algoritmo rápido de grabación de una memoria pasiva reprogramable EPROM

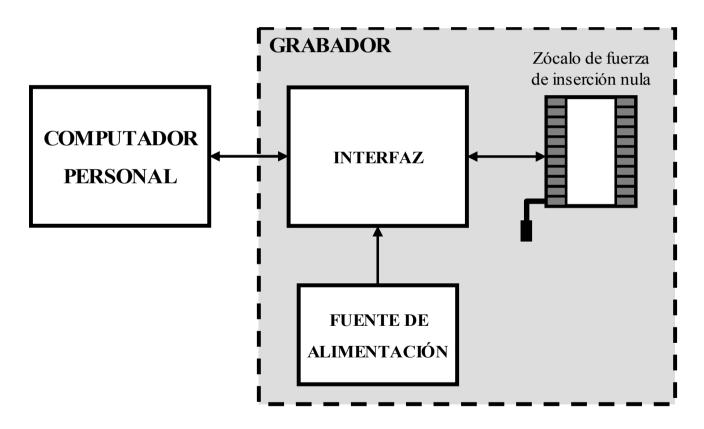

Esquema de bloques de un grabador de memorias pasivas reprogramables EPROM

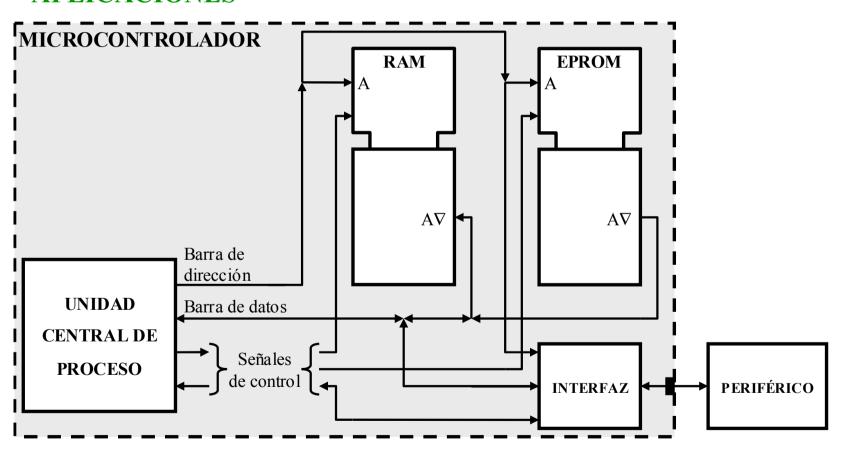

Aplicación de las memorias pasivas reprogramables EPROM al almacenamiento de las instrucciones de un microcomputador

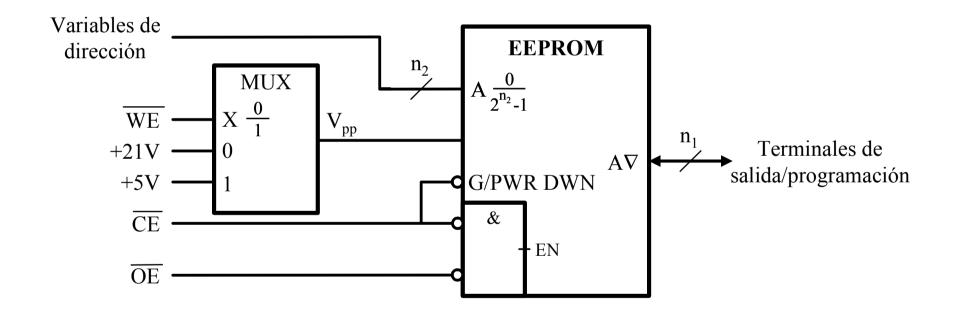

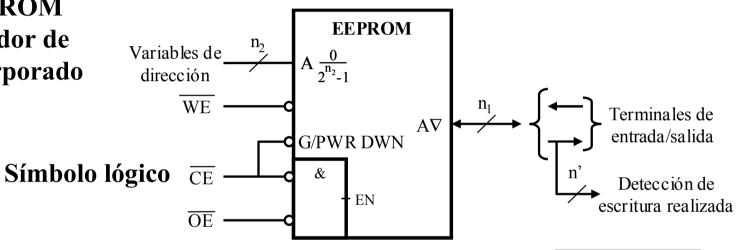

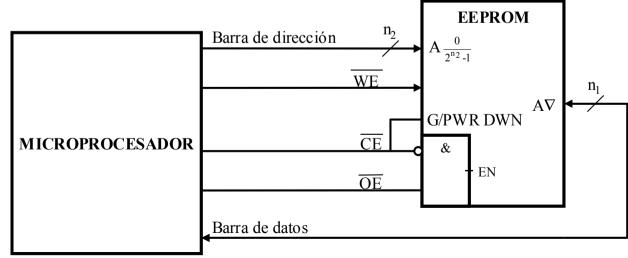

Símbolo lógico de una memoria pasiva reprogramable EEPROM con terminal de impulsos de grabación  $(V_{PP})$

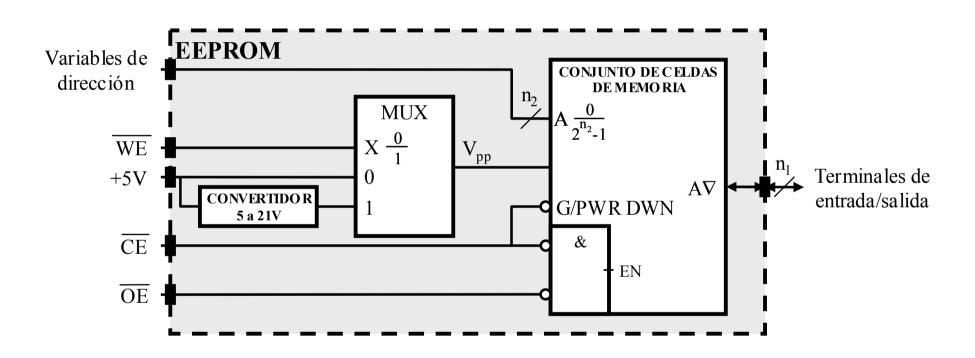

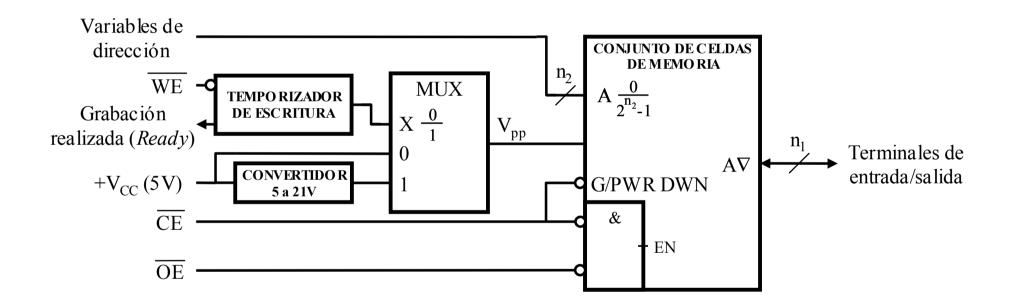

Esquema de bloques de una memoria pasiva reprogramable EEPROM con tensión de alimentación única

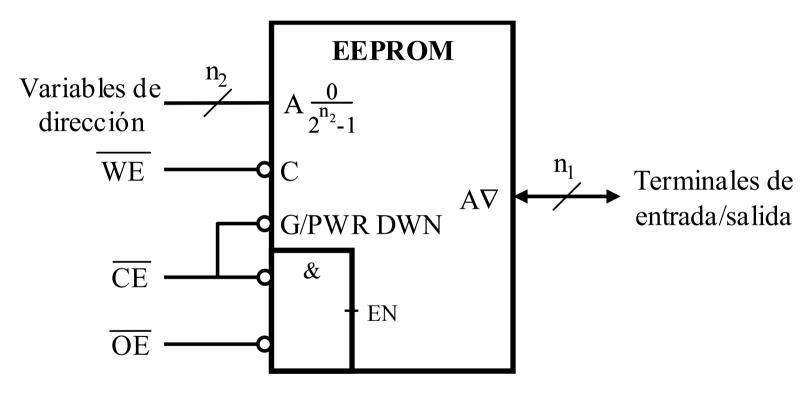

Símbolo lógico de una memoria pasiva reprogramable EEPROM con tensión de alimentación única

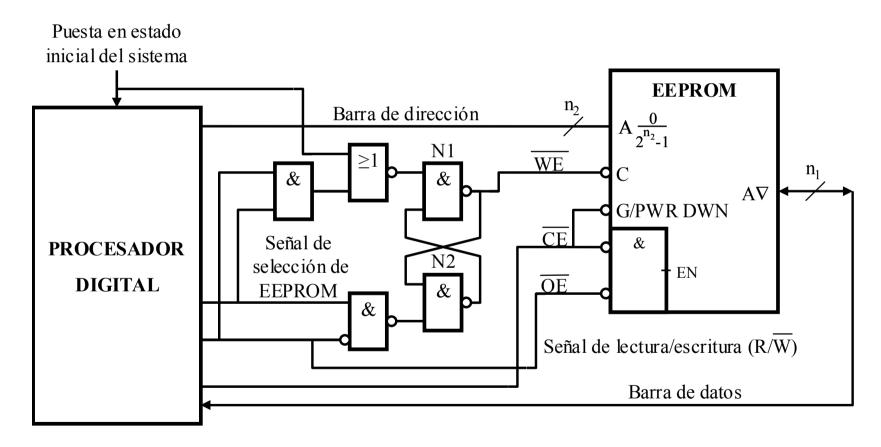

Circuito de conexión de la memoria pasiva reprogramable EEPROM con tensión de alimentación única a un procesador digital

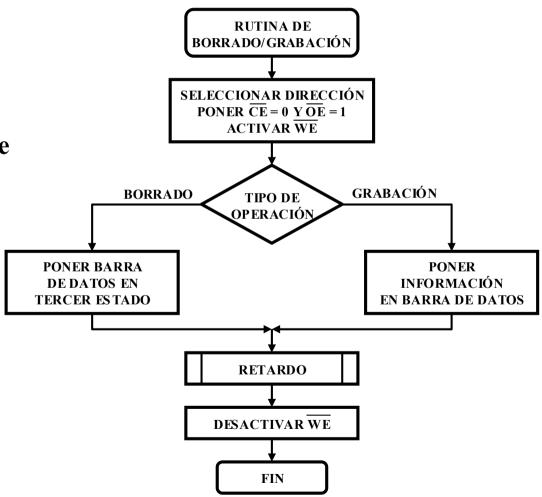

Algoritmo de grabación

de la memoria de acceso

aleatorio pasiva reprogramable

EEPROM

Esquema de bloques de una memoria pasiva reprogramable EEPROM con temporizador de escritura incorporado

Memoria EEPROM con temporizador de escritura incorporado

Conexión a un microprocesador

Aplicación de las memorias EEPROM al almacenamiento de tablas

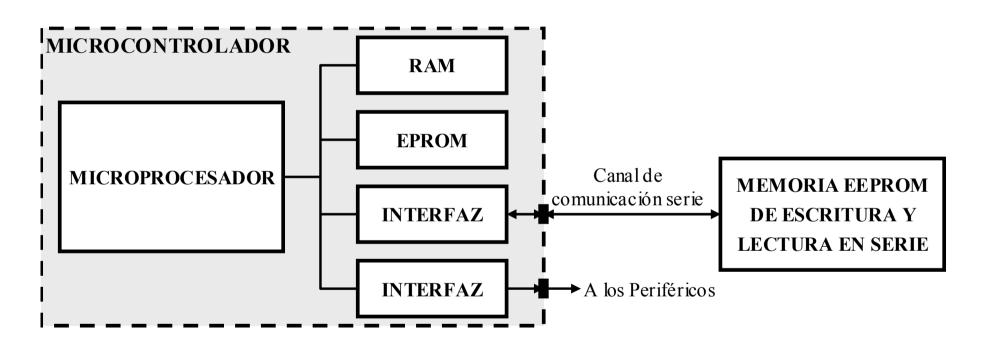

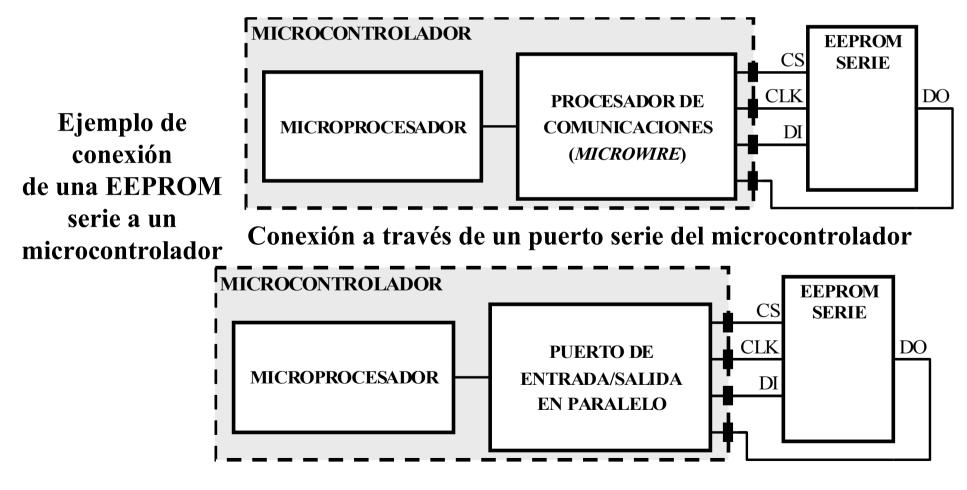

Conexión de un microcontrolador y una memoria EEPROM de lectura y escritura en serie (Serial EEPROM)

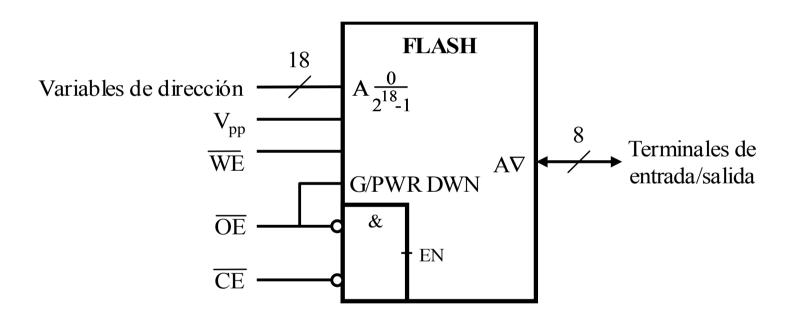

Símbolo lógico de una memoria FLASH

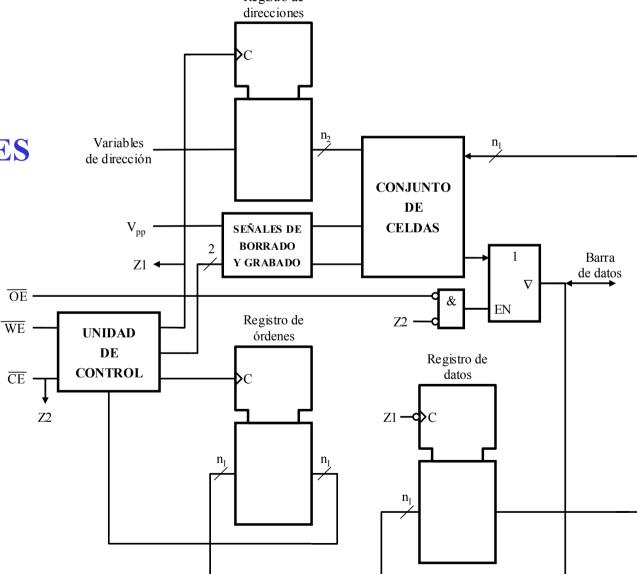

#### MEMORIAS DE ACCESO ALEATORIO

MEMORIAS

PASIVAS

REPROGRAMABLES

FLASH

Esquema de bloques simplificado de una memoria FLASH

### MEMORIAS DE ACCESO ALEATORIO MEMORIAS PASIVAS REPROGRAMABLES FLASH

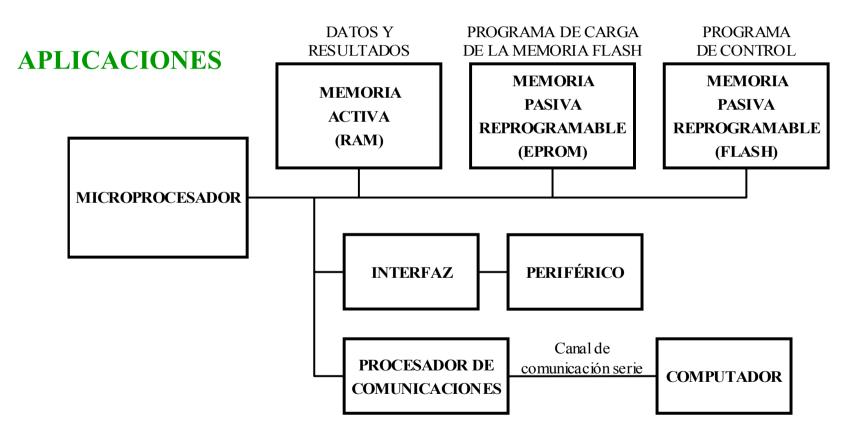

Aplicación de las memorias FLASH al almacenamiento de programas en un sistema de control distribuido

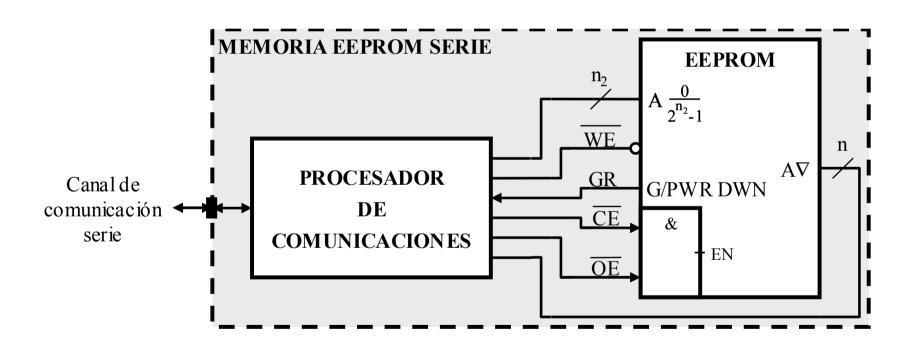

# MEMORIAS DE ACCESO ALEATORIO MEMORIAS DE ACCESO ALEATORIO DE COMUNICACIÓN SERIE

Esquema de bloques de una memoria de acceso aleatorio de lectura y escritura en serie

# MEMORIAS DE ACCESO ALEATORIO MEMORIAS EEPROM DE COMUNICACIÓN SERIE

## MEMORIAS DE ACCESO ALEATORIO MEMORIAS EEPROM DE COMUNICACIÓN SERIE

Conexión a través de un puerto paralelo del microcontrolador

#### MEMORIAS DE ACCESO ALEATORIO

#### MEMORIAS EEPROM CON COMUNICACIÓN SERIE

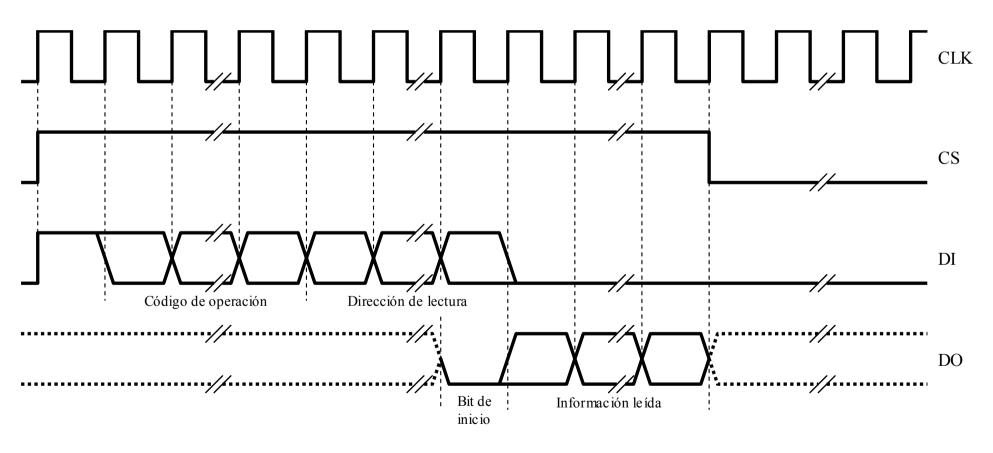

Cronograma del ciclo de lectura de las señales de una memoria EEPROM que utiliza el protocolo *Microwire*

#### MEMORIAS DE ACCESO ALEATORIO MEMORIAS DE ACCESO ALEATORIO CON COMUNICACIÓN SERIE

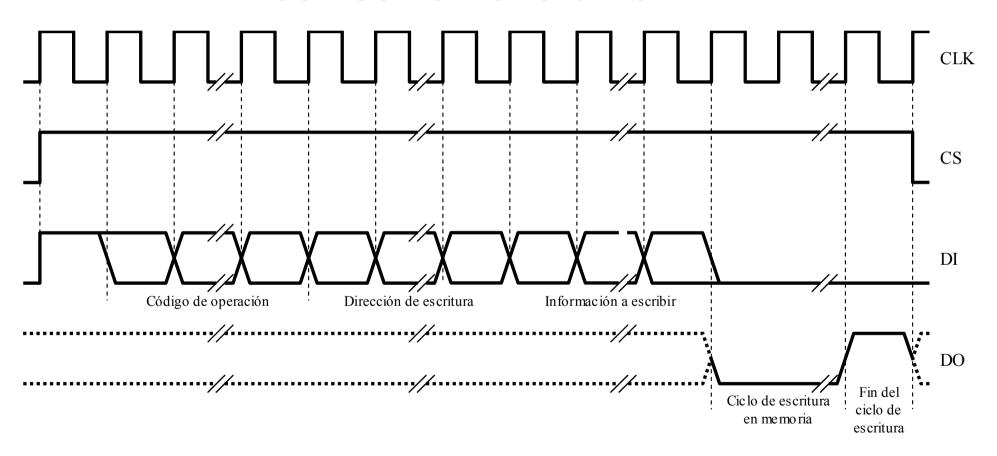

Cronograma del ciclo de escritura de las señales de una memoria EEPROM que utiliza el protocolo *Microwire*

# MEMORIAS DE ACCESO ALEATORIO MEMORIAS DE ACCESO ALEATORIO CON COMUNICACIÓN SERIE

#### **APLICACIONES**

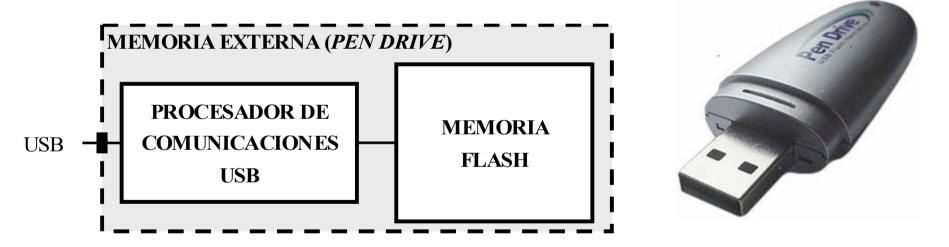

Esquema de bloques

Fotografía

Memoria externa (Pen Drive) conectable a un computador mediante el protocolo de comunicaciones USB

#### MEMORIAS DE ACCESO ALEATORIO MEMORIAS DE ACCESO ALEATORIO CON COMUNICACIÓN SERIE

#### **APLICACIONES**

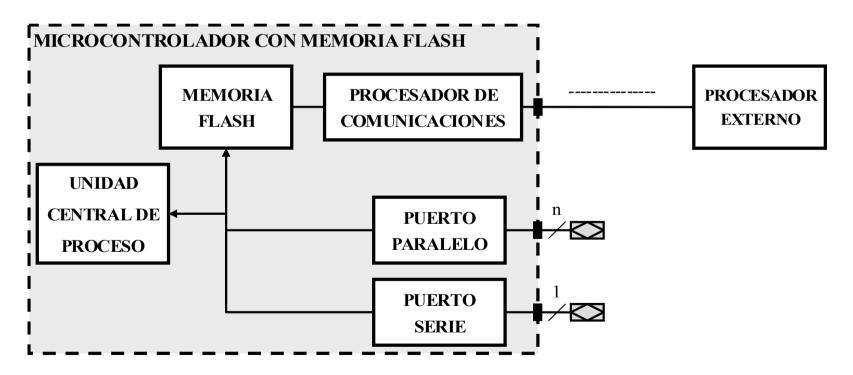

Microcontrolador que almacena las instrucciones en una memoria FLASH

### MEMORIAS DE ACCESO ALEATORIO UNIDADES DE MEMORIA MODULARES

Símbolo lógico de una memoria de acceso aleatorio activa, estática y de escritura y lectura no simultáneas con terminales de entrada y salida comunes

#### Electrónica Digital: Unidades de memoria digitales

#### MEMORIAS DE ACCESO ALEATORIO

#### UNIDADES DE MEMORIA MODULARES

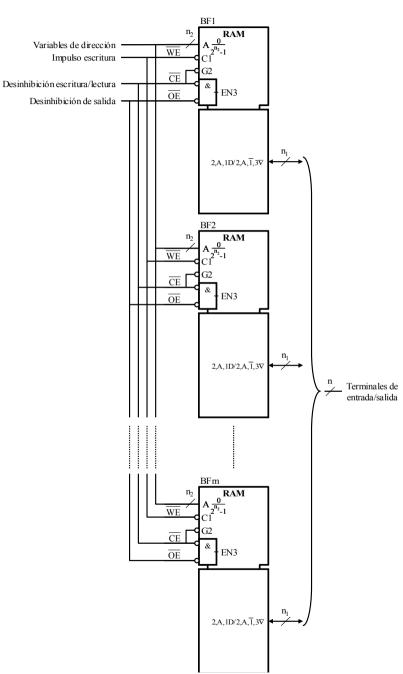

Unidad de memoria de acceso aleatorio activa de  $2^{n^2}$  posiciones de  $n'_1$ bits implementada con n' bloques funcionales idénticos

#### Electrónica Digital: Unidades de memoria digitales

#### MEMORIAS DE ACCESO ALEATORIO

#### UNIDADES DE MEMORIA MODULARES

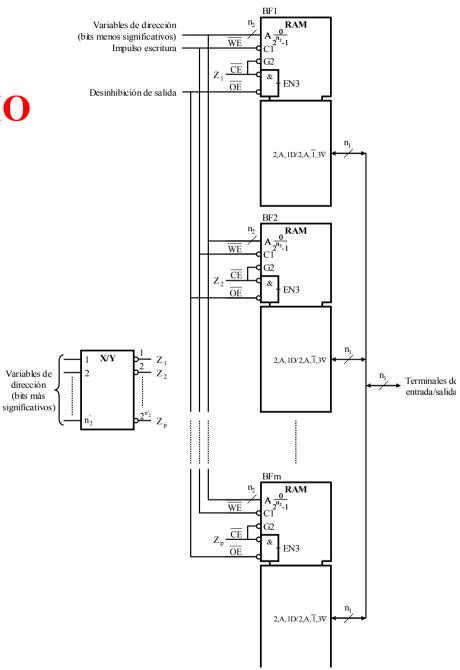

Unidad de memoria de acceso aleatorio activa de *m* posiciones de *n*1 bits implementada con  $2^{n'}_{2}$  bloques funcionales idénticos

#### MEMORIAS DE ACCESO ALEATORIO

#### UNIDADES DE MEMORIA MODULARES

Símbolo lógico de una memoria de acceso aleatorio activa estática de escritura y lectura no simultáneas de 256 posiciones de 4 bits

### MEMORIAS DE ACCESO ALEATORIO UNIDADES DE MEMORIA MODULARES

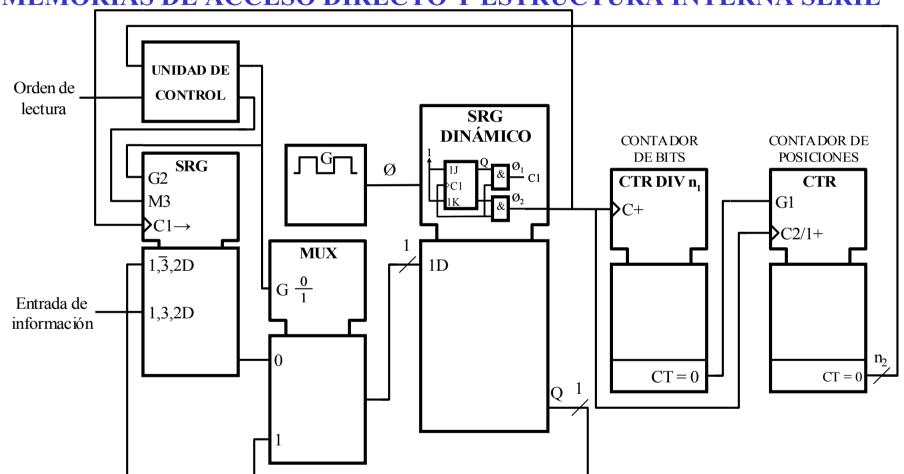

#### MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

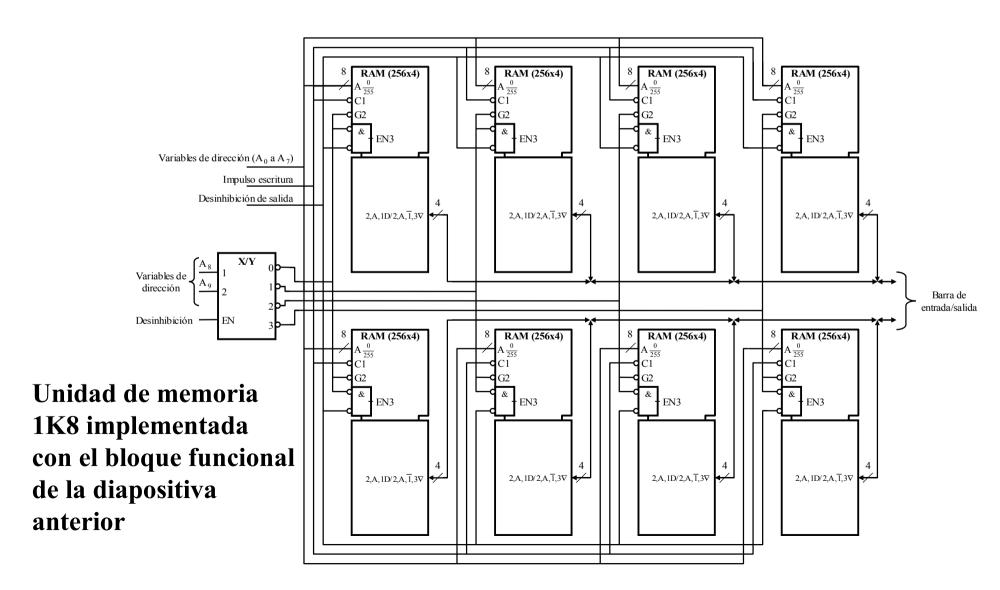

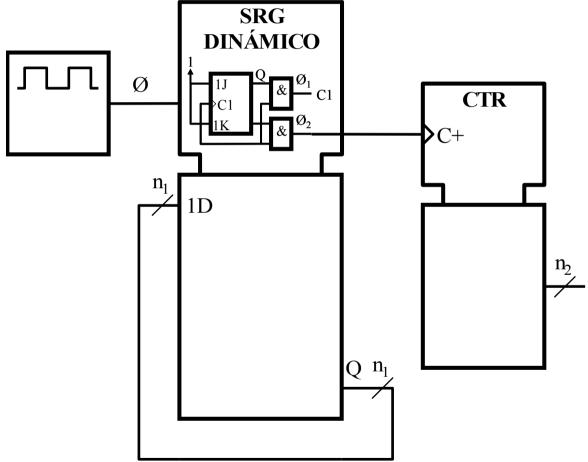

Esquema básico de un registro de desplazamiento dinámico utilizado como memoria de acceso directo

#### MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

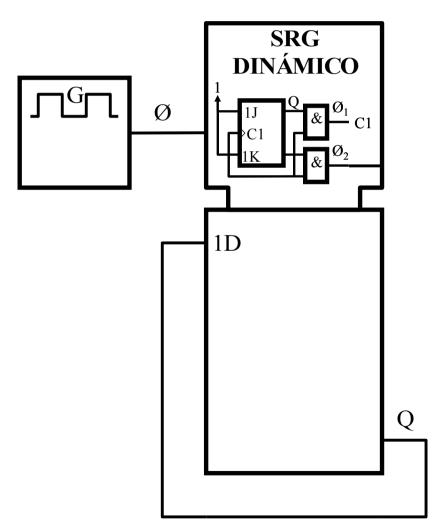

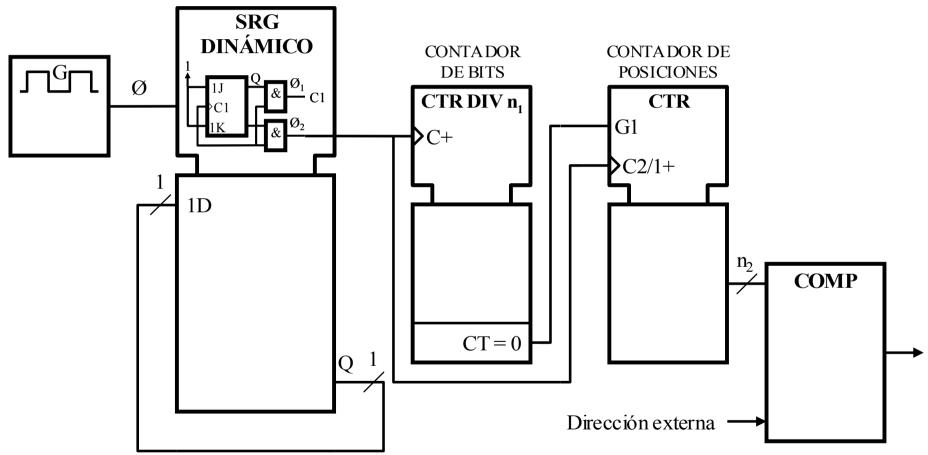

Esquema básico de una memoria de acceso directo implementada mediante un registro de desplazamiento dinámico y un contador y organizada en posiciones de n<sub>1</sub> bits

#### MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

Esquema básico de una memoria de acceso directo implementada mediante un registro de desplazamiento dinámico y un contador y organizada en serie bit a bit

#### MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

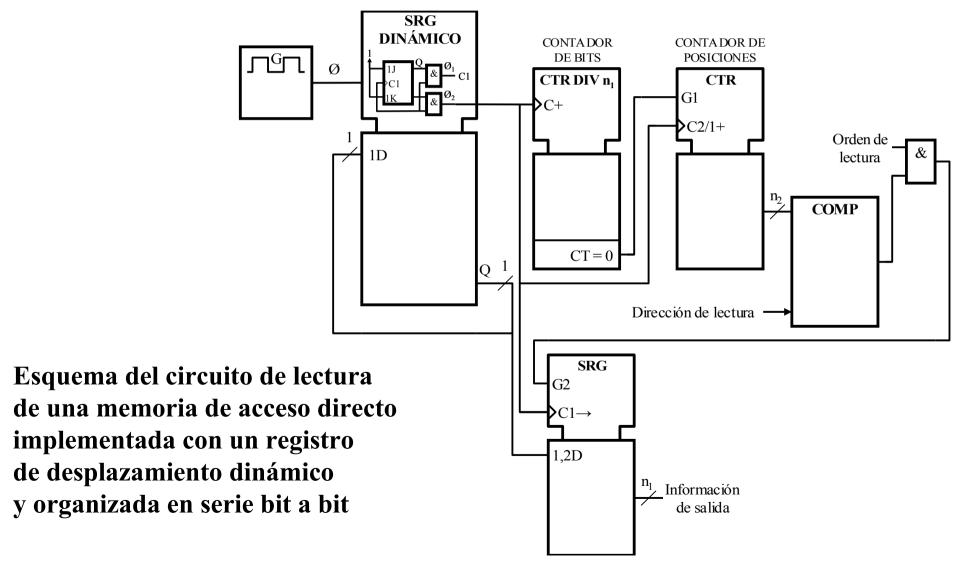

#### MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

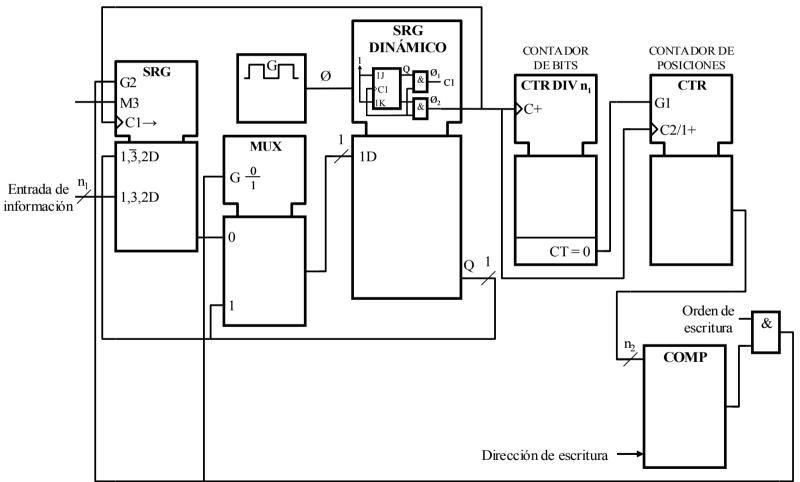

Esquema del circuito de escritura de una memoria de acceso directo implementada con un registro de desplazamiento dinámico y organizada en serie bit a bit

#### MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

Esquema del circuito de escritura secuencial de una memoria de acceso directo implementada con un registro de desplazamiento dinámico y organizada en serie bit a bit

## MEMORIAS DE ACCESO SECUENCIAL CARACTERISTICAS GENERALES

Memorias que se caracterizan por carecer de variables de dirección. En ellas no se especifica la dirección sino que en la operación de escritura la información se introduce en la posición de la memoria conectada a los terminales de entrada y en la de lectura se lee la situada en la posición unida a los terminales de salida. Este tipo de memorias tiene como objetivo facilitar el tratamiento de la información proporcionada en secuencia por un sistema digital. Según la forma en la que se accede a la información almacenada se pueden clasificar en tres grandes clases:

- Registros de desplazamiento.

- Memorias cola o tubo.

- Memorias pila

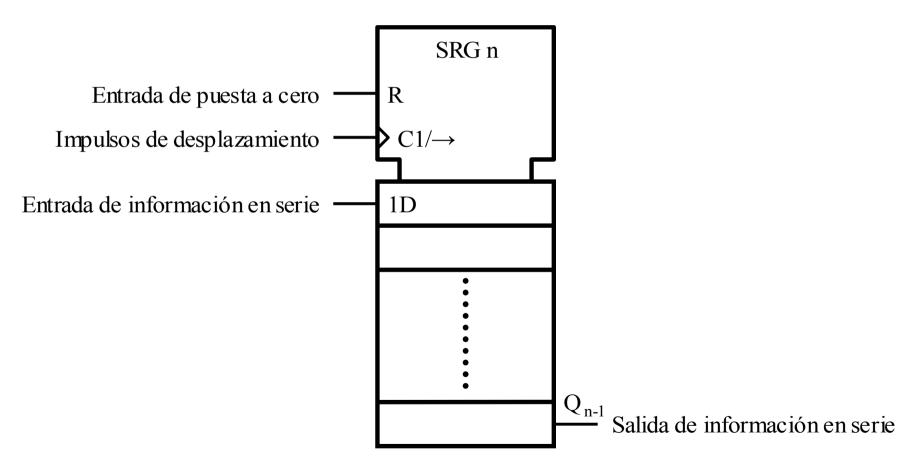

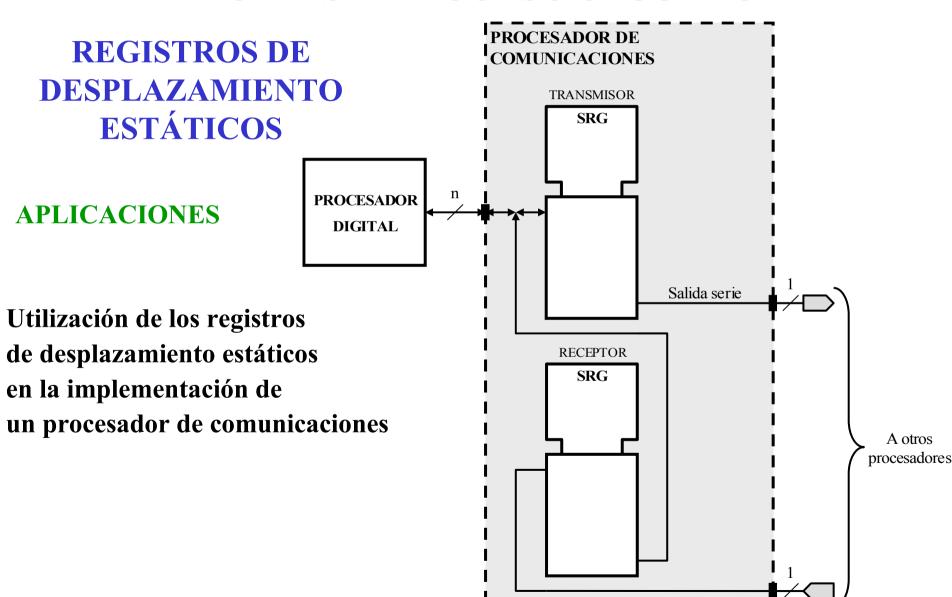

#### MEMORIAS DE ACCESO SECUENCIAL REGISTROS DE DESPLAZAMIENTO ESTÁTICOS

Símbolo lógico de un registro de desplazamiento estático

# MEMORIAS DE ACCESO SECUENCIAL REGISTROS DE DESPLAZAMIENTO DINÁMICOS

Se caracterizan porque los impulsos de desplazamiento no se pueden anular por tiempo indefinido dado que en dicho caso desaparece la información contenida en su interior. Se han realizado especialmente en tecnologías MOS y están formados por celdas básicas de memoria que almacenan la información en forma de carga del condensador existente entre la puerta y el surtidor de un transistor MOS. Se utilizan para implementar Memorias circulares.

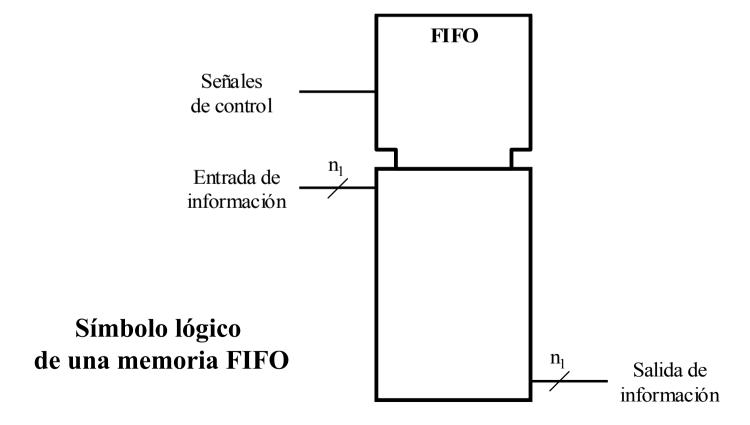

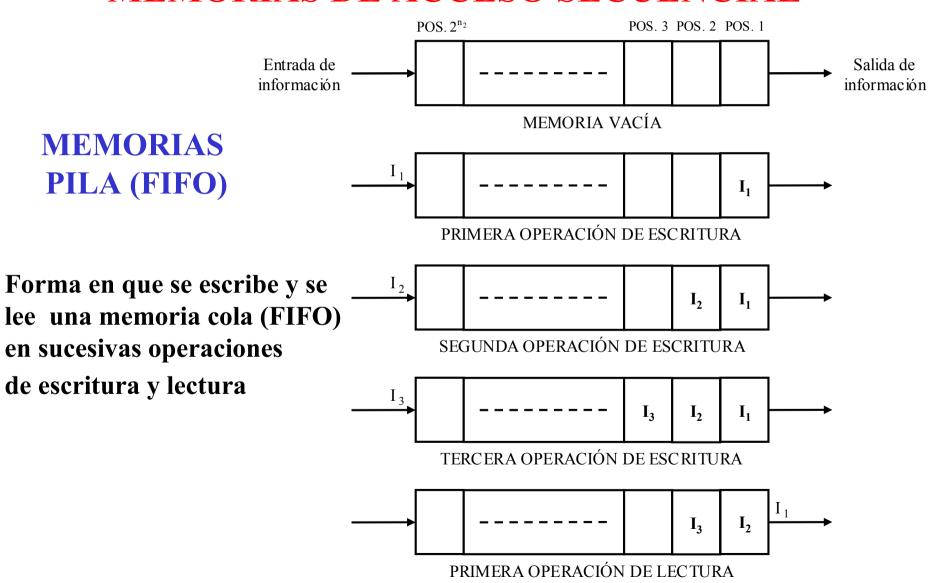

## MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (FIFO)

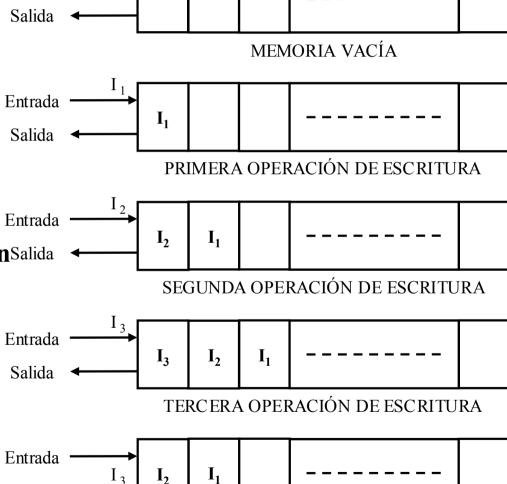

Son memorias de acceso secuencial en las que la información que entra al darle una orden de escritura sale antes que todas las que entran en posteriores ordenes de escritura.

#### MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (FIFO)

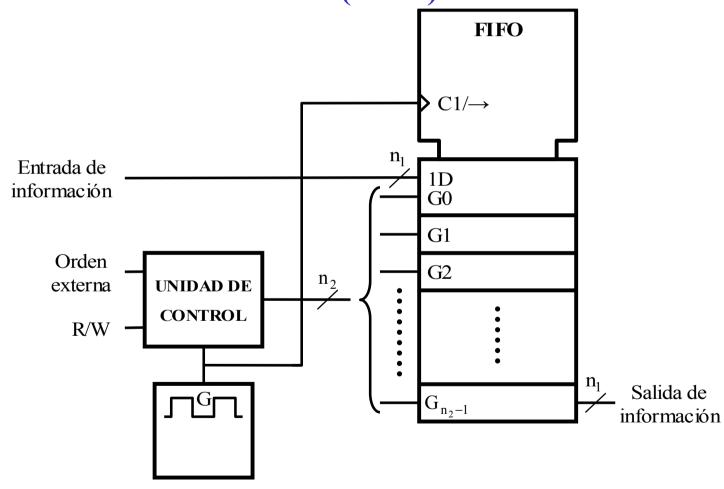

Memoria cola (FIFO) implementada mediante un conjunto de biestables conectados en serie con entradas de inhibición independientes

# MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (FIFO) IMPLEMENTADAS CON UNA MEMORIA DE ESTRUCTURA INTERNA SERIE

Poseen las siguientes características que limitan su operatividad:

- -En ellas la información se desplaza físicamente lo cual hace que su escritura necesite tantos impulsos del reloj como posiciones vacías posea la memoria.

- -La elevación de su número de posiciones disminuye su velocidad porque aumenta el tiempo medio de escritura.

- -No es posible realizar en operaciones de lectura y escritura simultáneas.

- -No es posible realizar dos lecturas sucesivas de la misma posición.

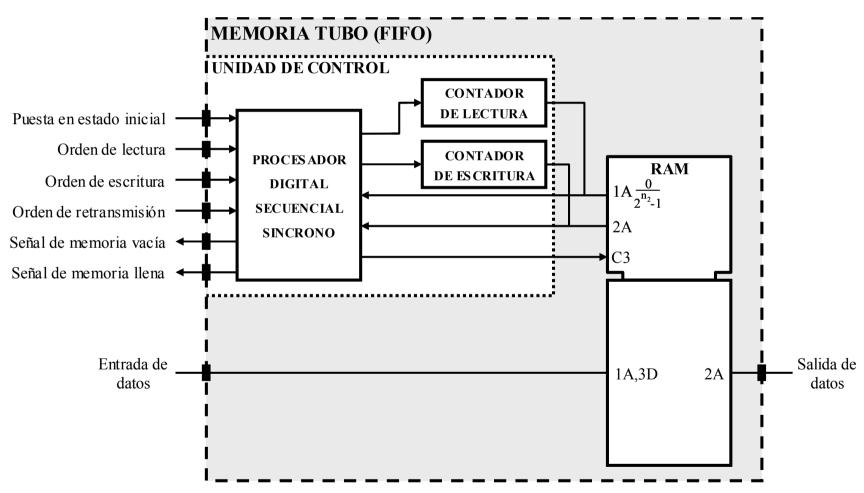

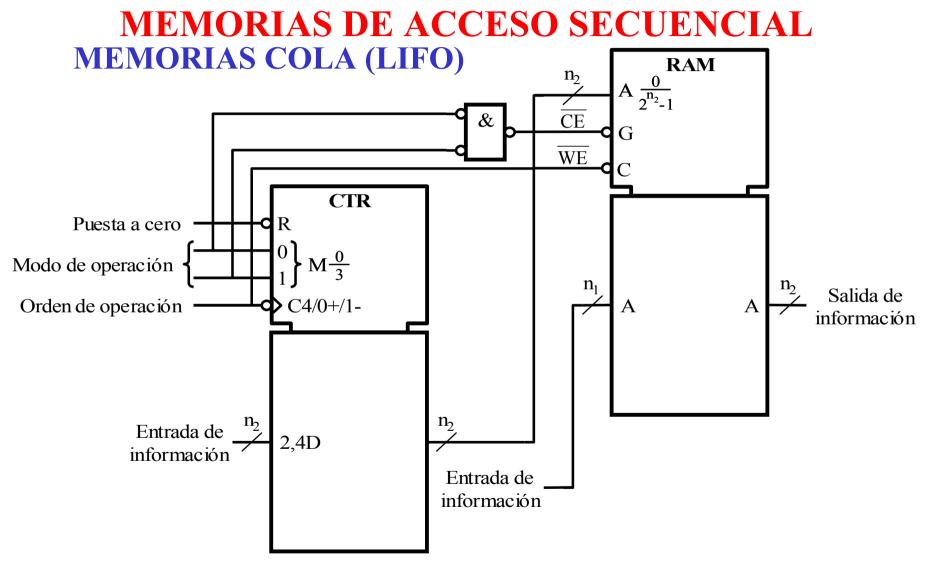

### MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (FIFO) IMPLEMENTADAS CON UNA RAM

Esquema de bloques de una memoria cola (FIFO) implementada mediante una memoria de acceso aleatorio de lectura y escritura simultáneas.

#### MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (FIFO) IMPLEMENTADAS CON UNA RAM

#### Poseen las siguientes características:

- Todas las operaciones de escritura tienen idéntica duración.

- Es posible realizar la operación de escritura y la de lectura simultáneamente.

- Se puede ampliar la capacidad de la memoria sin disminuir la velocidad.

- Es posible realizar varias operaciones de lectura sucesivas de una o más posiciones de la memoria consecutivas. Para ello se dota a la memoria de un terminal que hace que el contenido del contador de lectura disminuya en una unidad. Dicho terminal suele denominarse orden de retransmisión porque su principal utilidad es hacer que se vuelva a enviar la información contenida en la memoria cuando la misma forma parte de un procesador de comunicaciones en la aplicación descrita a continuación.

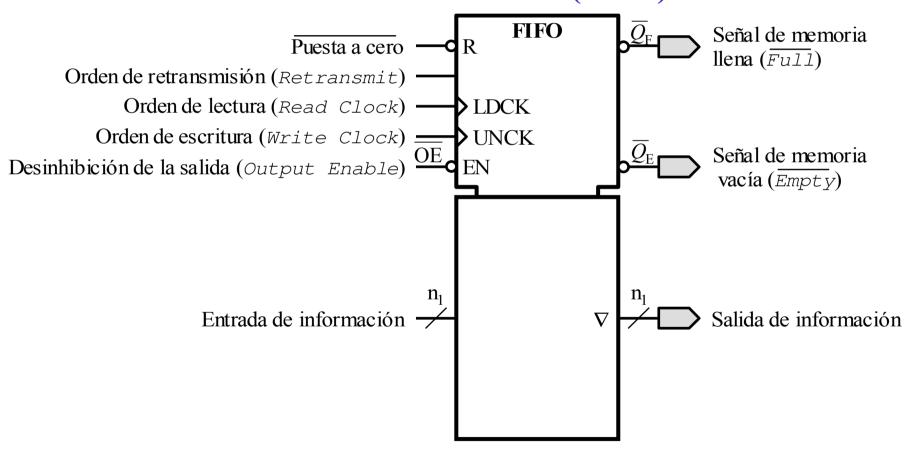

- Existen múltiples alternativas que se diferencian por las señales de control que la acoplan con los sistemas externos

#### **MEMORIAS COLA (FIFO)**

Símbolo lógico de una memoria cola (FIFO) implementada mediante una memoria de acceso aleatorio de lectura y escritura simultáneas..

#### **MEMORIAS COLA (FIFO)**

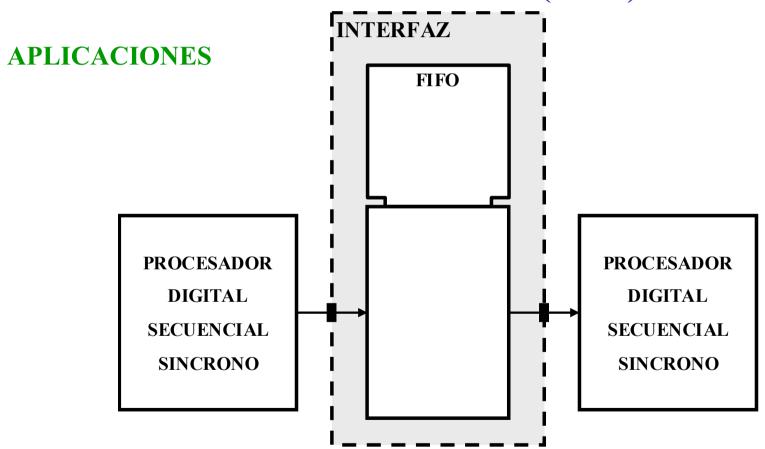

Esquema básico del acoplamiento entre dos procesadores digitales síncronos implementado mediante una memoria cola

### MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (FIFO)

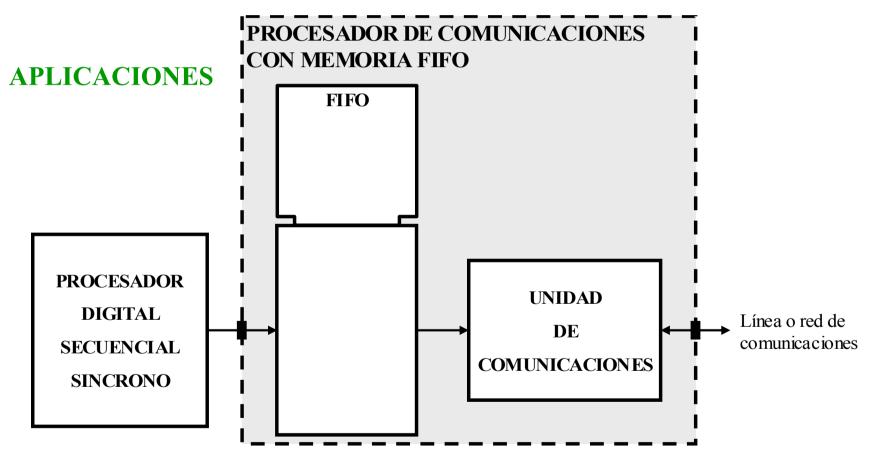

Esquema de bloques básico del acoplamiento de un procesador digital secuencial síncrono a una línea o red de comunicaciones por medio de un procesador de comunicaciones que posee una memoria cola (FIFO)

#### **MEMORIAS COLA (FIFO)**

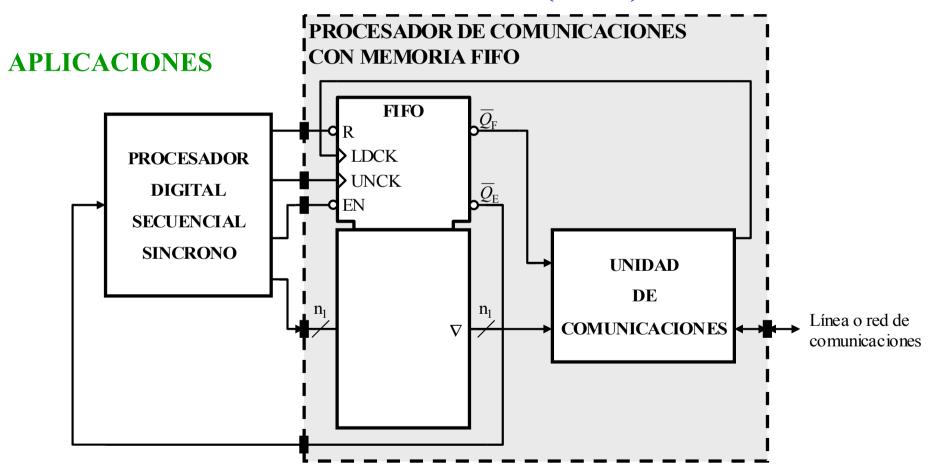

Esquema de bloques de un procesador de comunicaciones implementado con una memoria cola

Entrada

Salida

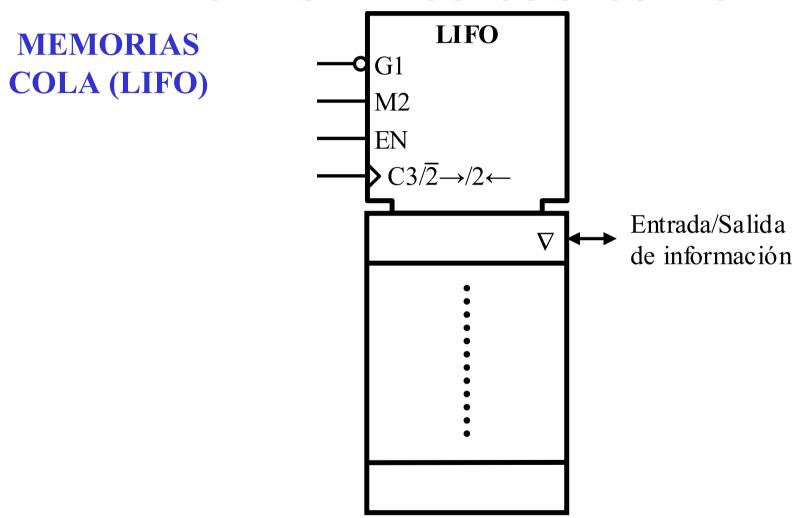

#### **MEMORIAS PILA (LIFO)**

Las memorias pila (Stack)

conocidas como LIFO

(acrónimo de Last In-First Out)

son memorias de acceso secuencial

en las que la información que entra

en la última operación de escritura

es la que sale en la primera operación Salida

de lectura que se realice.

Forma en que se escribe y se lee una memoria pila (LIFO) en sucesivas operaciones de escritura y lectura.

PRIMERA OPERACIÓN DE LECTURA

# MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (LIFO)

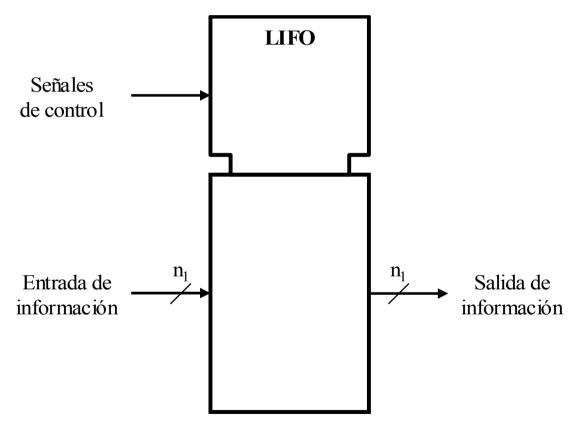

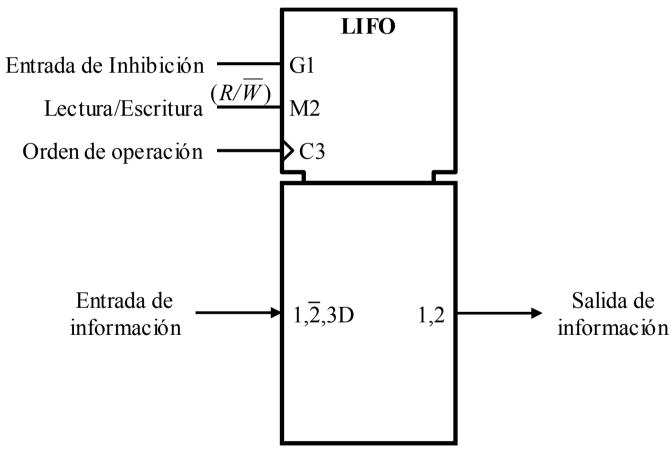

Símbolo lógico básico de una memoria cola (LIFO) organizada en posiciones de n1 bits en paralelo

# MEMORIAS DE ACCESO SECUENCIAL MEMORIAS COLA (LIFO)

Símbolo lógico de una memoria cola (LIFO) organizada en posiciones de n<sub>1</sub> bits en paralelo

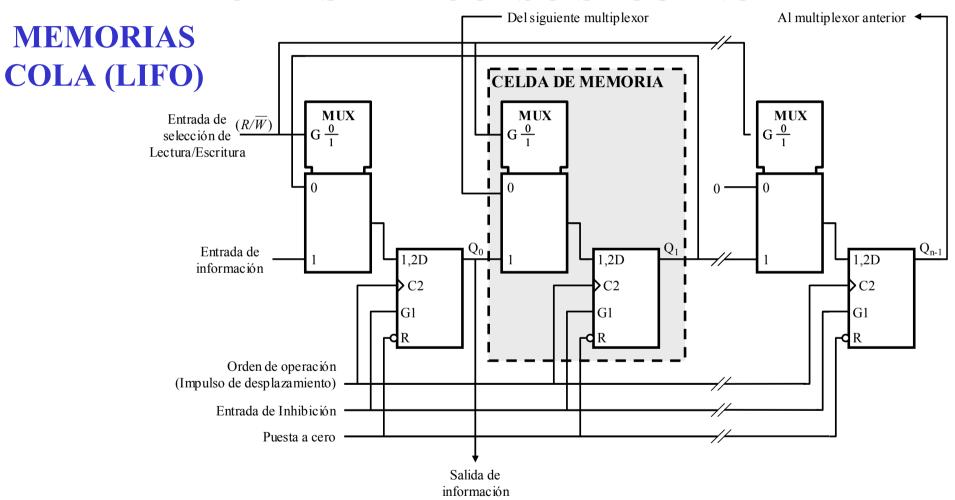

Esquema de una memoria PILA implementada con un registro de desplazamiento estático reversible

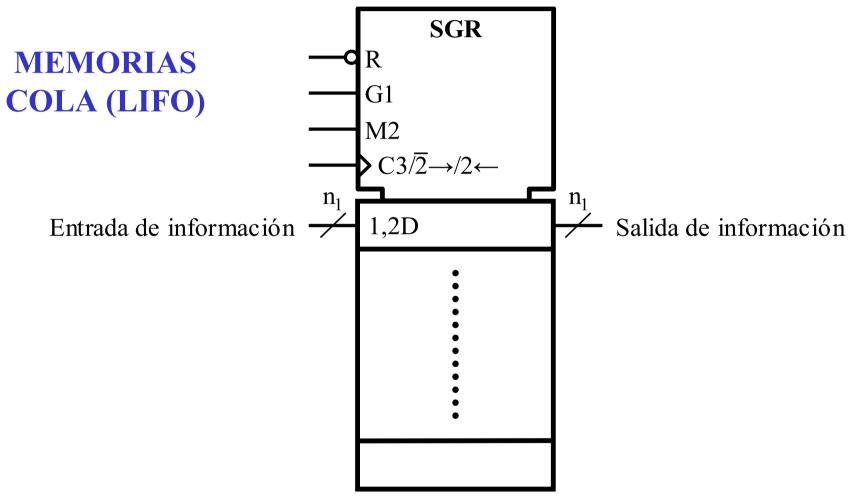

Símbolo lógico de una memoria pila de n<sub>1</sub> bits en paralelo implementada con un registro de desplazamiento

Símbolo lógico de una memoria pila de n<sub>1</sub> bits en paralelo y terminales de entrada y salida únicos

Esquema básico de una memoria PILA implementada con una memoria de acceso aleatorio

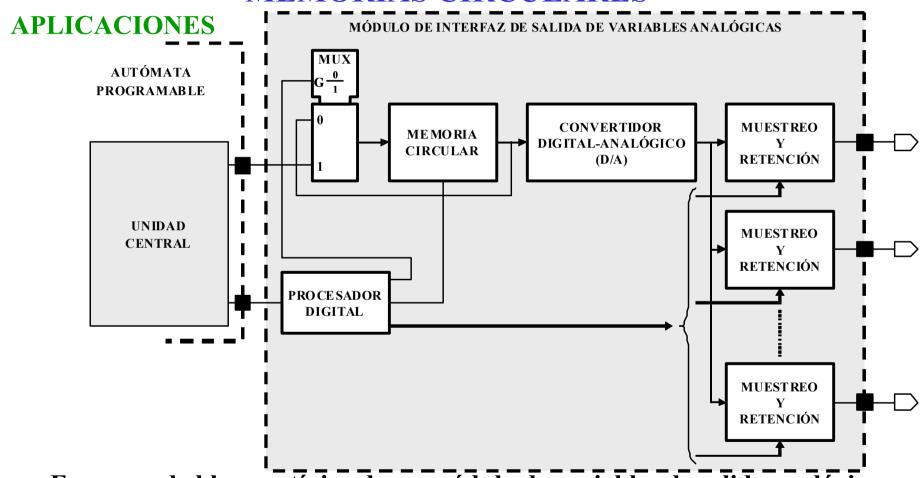

### MEMORIAS DE ACCESO DIRECTO Y SECUENCIAL MEMORIAS CIRCULARES

Se puede definir una memoria circular como una memoria de acceso secuencial en la que la información se desplaza permanentemente a través de la memoria cuando no se ejecuta ninguna operación de entrada o de salida.

Son numerosos los fabricantes de sistemas electrónicos digitales que denominan memorias circulares a las que tienen acceso directo en la operación de escritura y acceso secuencial en la de lectura.

### MEMORIAS DE ACCESO DIRECTO Y SECUENCIAL MEMORIAS CIRCULARES

Esquema de bloques típico de un módulo de variables de salida analógicas de un autómata programable realizado con una memoria circular y un único convertidor analógico/digital

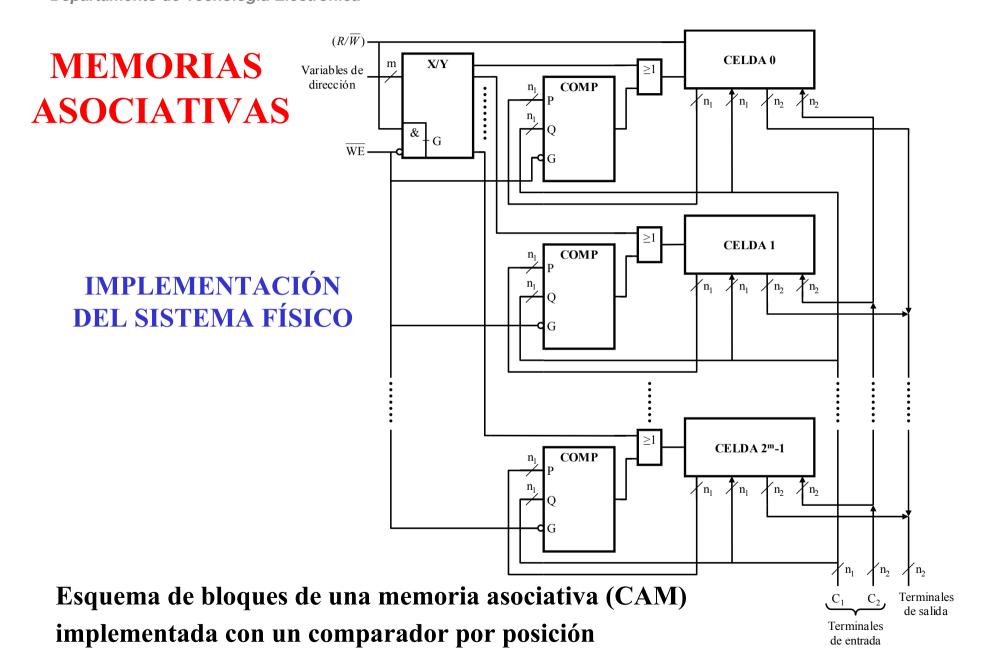

# MEMORIAS ASOCIATIVAS DESCRIPCIÓN GENERAL

Se conocen mediante las siglas CAM (Content Addressable Memories) y se caracterizan porque la búsqueda de información en la operación de lectura no se realiza indicando una dirección y leyendo su contenido sino que se suministra la información a la memoria para observar si ésta la contiene en alguna de sus posiciones.

#### Se pueden implementar:

- Con un comparador por posición.

- Con un único comparador.

#### **MEMORIAS ASOCIATIVAS**

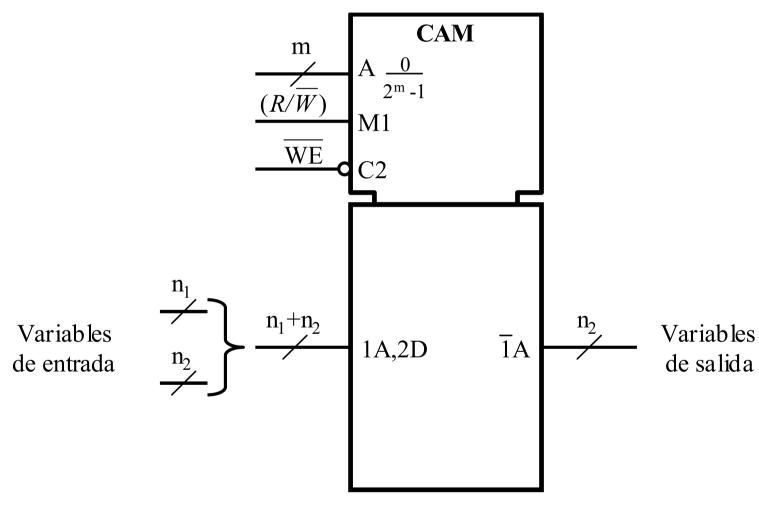

Símbolo lógico de una memoria asociativa (CAM) implementada con un comparador por posición

#### **MEMORIAS ASOCIATIVAS**

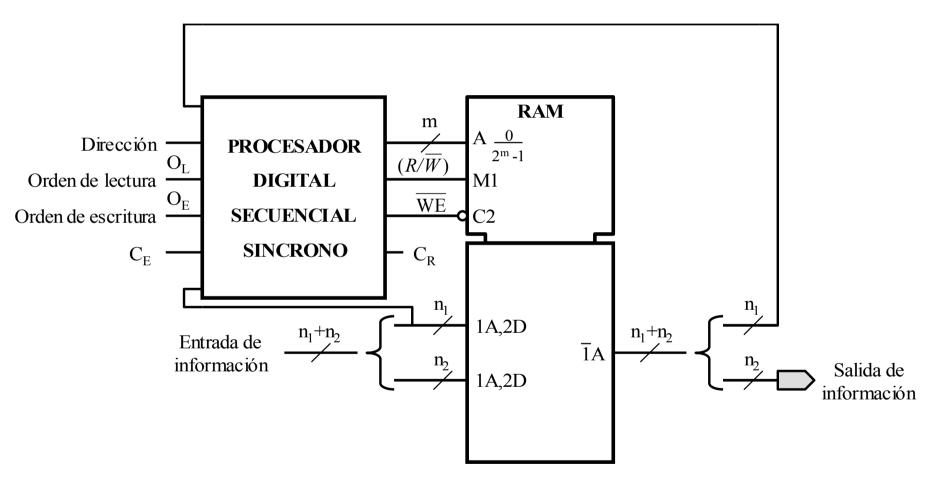

Esquema de bloques de una memoria asociativa (CAM) implementada con un procesador digital secuencial síncrono (un único comparador).