| | Modo Standard | Modo Fast | |

| Parámetro | Símbolo | MIN | MAX | MIN | MAX | Unidad |

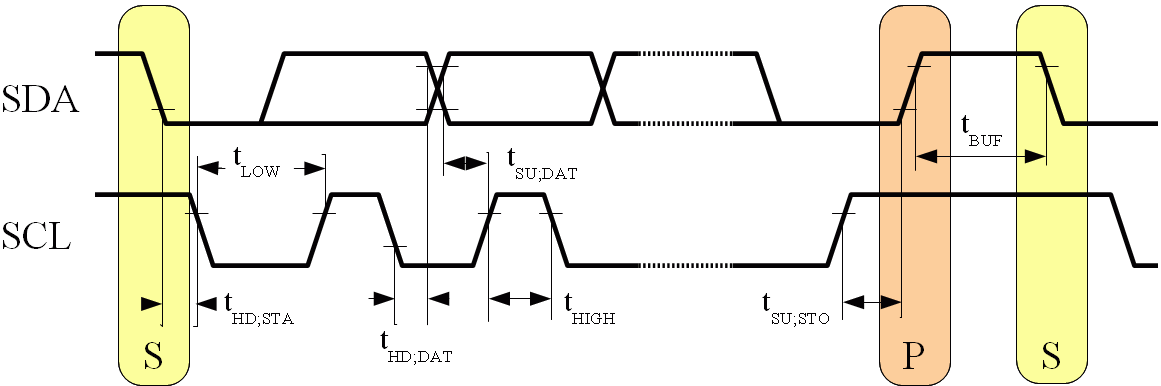

| Tiempo Hold de START. Tras él se genera el primer pulso de SCL. En la condición de START, tiempo que debe transcurrir entre el flanco de bajada de SDA y el flanco de bajada de SCL. | tHD;STA | 4 | - | 0.6 | - | μs |

| Duración del semiperíodo BAJO del reloj SCL | tLOW | 4.7 | - | 1.3 | - | μs |

| Tiempo de almacenamiento del dato. Tiempo de mantenimiento del dato. Tiempo entre el flanco de bajada de SCL y el cambio del dato en SDA | tHD;DAT | | | | | |

| para masters CBUS compatibles | | 5.0 | - | - | - | μs |

| para dispositivos I2C | | 0 | 3.45 | 0 | 0.9 | μs |

| Tiempo set-up para los datos. Tiempo de puesta del dato. Tempo entre el cambio de datos en SDA y el próximo flanco de subida de SCL. Suele despreciarse. | tSU;DAT | 250 | - | 100 | - | ns |

| Duración del semiperíodo ALTO del reloj SCL | tHIGH | 4 | - | 0.6 | - | μs |

| Tiempo Set-up para STOP. En la condición de STOP, tiempo que debe transcurrir entre el flanco de subida de SCL y el flanco de subida de SDA | tSU;STO | 4 | - | 0.6 | - | μs |

| Tiempo bus libre entre STOP y START. Tiempo en el que el bus debe estar libre antes de comenzar una nueva transmisión. | tBUF | 4.7 | - | 1.3 | - | μs |

| Tiempo Set-up para START | tSU;STA | 4.7 | - | 0.6 | - | μs |

| Tiempo subida de SDA y SCL | tr | - | 1000 | 20 +0.1 Cb | 300 | ns |

| Tiempo bajada de SDA y SCL | tf | - | 300 | 20 +0.1 Cb | 300 | ns |