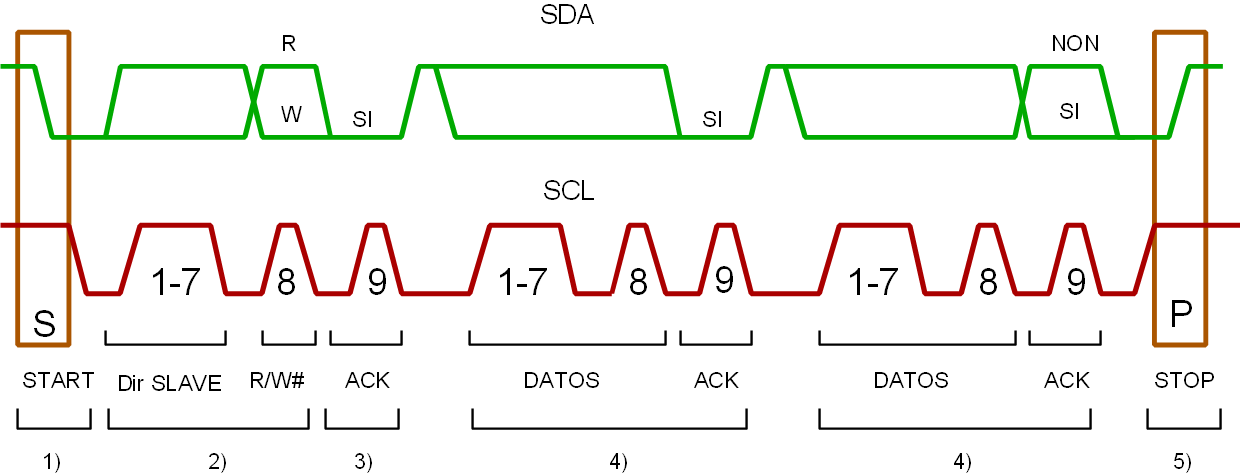

[Bus I2C] Protocolo

- 1) Bit de Inicio o

START: {SCL=1}, {SDA=↓, flanco de bajada}- Generado por el master.

- Un flanco de bajada en SDA mientras SCL esta a

1determina la condición de Inicio o Start. Medio periodo de reloj del master mas tarde SCL pasa a0y comienza una secuencia en SCL de 9 impulsos: Ver 2) y 3). - El Bus I2C se considera ocupado después de la condición de Inicio.

- 2) Primer byte: Dirección + Bit R/W

- También llamado byte de START, aunque puede dar lugar a confusión.

Dir SLAVEson los 7 bits de la dirección del esclavo con el que se quiere establecer comunicación. Recordar que primero se envía el bit de mayor peso.R/W#determina la dirección del mensaje, definiendo si el esclavo es transmisor o receptor.0: Escritura/Transmisión. El Master escribirá información en el esclavo.1: Lectura/Solicitud de datos. El Master leerá información del esclavo.

- Cuando un Master envía un byte tras la condición de Inicio, cada dispositivo comprueba los 7 primeros bits con su propia dirección. El que coincida se considera direccionado por el Master siendo un esclavo receptor o emisor según

R/W.

- 3) Bit

ACKReconocimiento- Precede al primer byte de datos. Lo provoca en SDA el receptor de datos, indicando su aceptación del byte precedente.

- El pulso de reloj correspondiente a este bit es generado por el Master.

- El transmisor desbloquea la línea SDA (

1) durante el pulso de reconocimiento. - El receptor debe poner a

0la línea SDA durante el pulsoACKde modo que siga siendo0durante el tiempo que el master genera el pulso1de SCL. Se trata pues, de un nivel0en SDA, que es liberada provisionalmente por el emisor durante el pulso 9 de SCL.

- 4) Byte mensaje + Bit

ACK- Mensaje dividido en octetos: 8 bits. El byte de datos se transfiere empezando por el bit de mayor peso o bit 7.

- Tras el byte de datos se produce otro bit de

ACK. - El nº de bytes que se envíen no tiene restricción, siempre seguidos por un

ACK. - En memorias I2C es normal que se envíen 2 bytes: Primero el de la dirección a la que acceder y luego el de la información que se grabe en dicha dirección (p.e.).

- 5) Bit Parada o

STOP: {SCL=1}, {SDA=↑, flanco de subida}- Generado por el master, que cambia SDA de

0a1mientras mantiene un1en SCL: Es un flanco de subida en SDA mientras SCL está a1. - El Bus se considera libre de nuevo después de un cierto tiempo tras el Stop.

- Sin embargo si un master todavía desea comunicarse con el bus, puede generar repetidamente condiciones de Start y direccionar a otro esclavo sin generar primero la condición de stop.